この記事では『Zetaコンバータ』について

- Zetaコンバータとは

- Zetaコンバータの原理・計算式・シミュレーション

などを図を用いて分かりやすく説明するように心掛けています。ご参考になれば幸いです。

Zetaコンバータとは

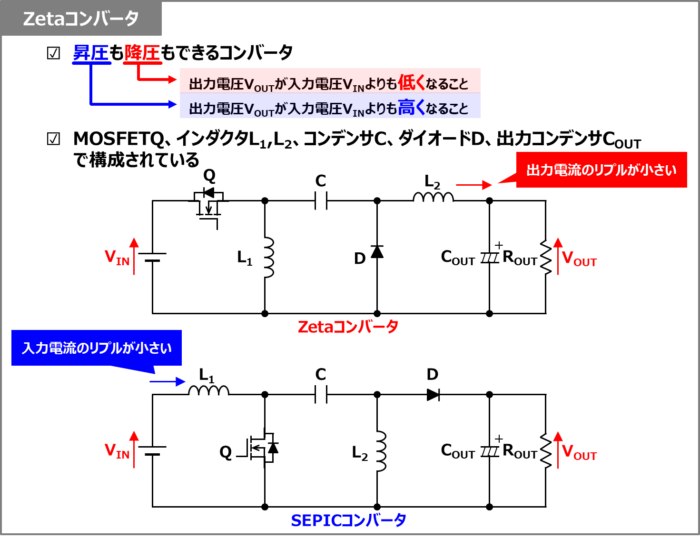

Zetaコンバータは、昇圧も降圧もできるコンバータです。

- 昇圧:出力電圧\(V_{OUT}\)が入力電圧\(V_{IN}\)よりも高くなること

- 降圧:出力電圧\(V_{OUT}\)が入力電圧\(V_{IN}\)よりも低くなること

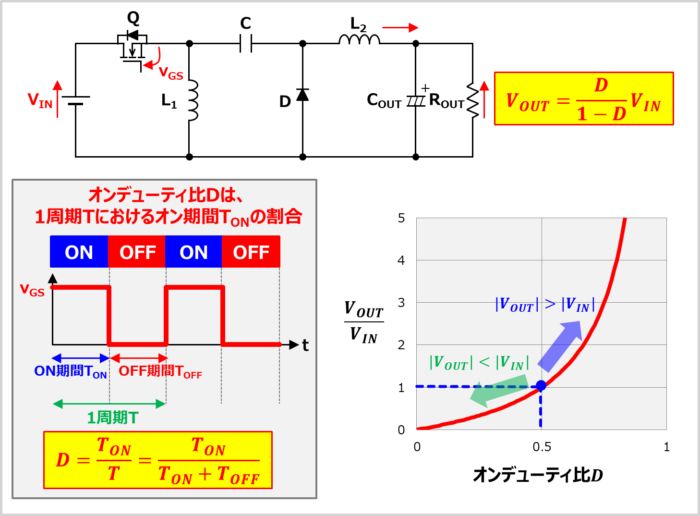

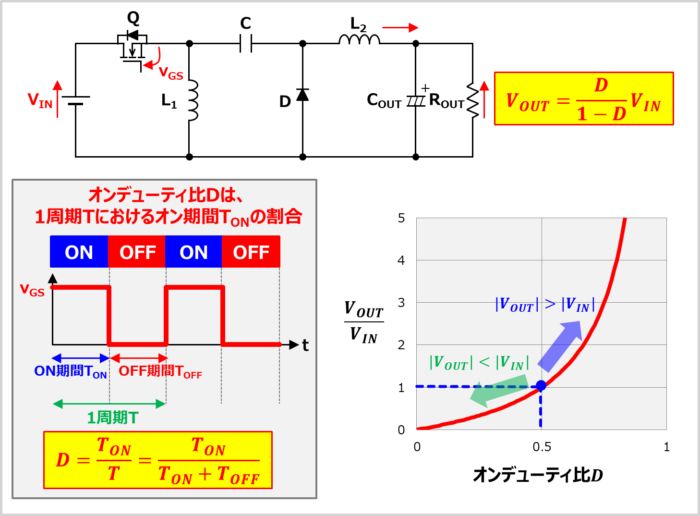

Zetaコンバータは、MOSFET\(Q\)、インダクタ\(L_1,L_2\)、コンデンサ\(C\)、ダイオード\(D\)、出力コンデンサ\(C_{OUT}\)で構成されています。

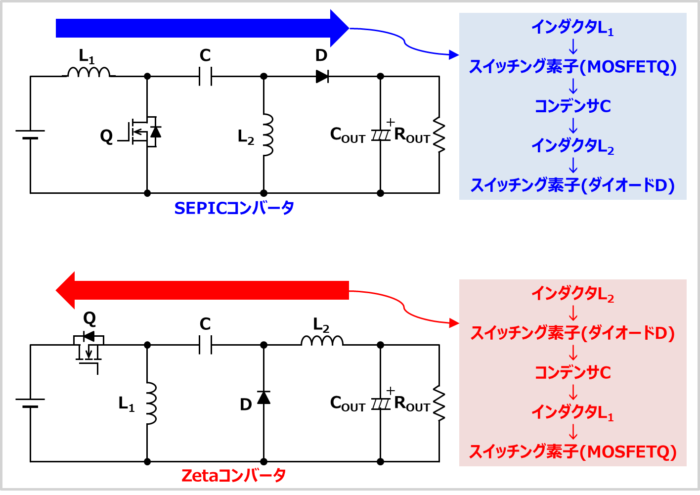

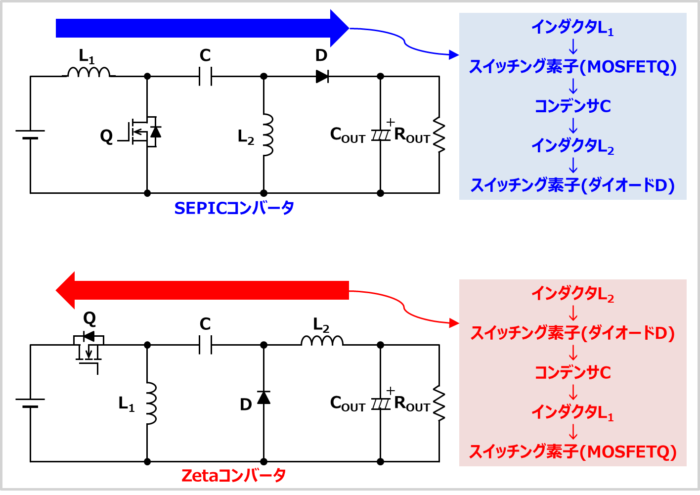

ZetaコンバータはInverse SEPIC(反転SEPIC)との別名があり、SEPICコンバータの入力と出力を反転させ、MOSFET\(Q\)とダイオード\(D\)を入れ替えた回路形態となっています。

SEPICコンバータは入力側にインダクタ\(L_1\)があるため、入力電流のリプルが小さくなるというメリットがありますが、出力電流のリプルが大きくなります。

一方、ZetaコンバータはSEPICコンバータと真逆で、出力側にインダクタ\(L_2\)があるため、出力電流のリプルが小さくなるというメリットがありますが、入力電流のリプルが大きくなります。

下記にZetaコンバータのメリットとデメリットをまとめます。

メリット

- 昇圧も降圧も可能。

- 入力電圧\(V_{IN}\)と出力電圧\(V_{OUT}\)が同極性。

- 出力電流のリプルが小さい。

- コンデンサ\(C\)により、入力と出力を分離しているため、出力部の短絡に強い。

→そのため、出力コンデンサ\(C_{OUT}\)の容量を小さくすることができる(出力コンデンサ\(C_{OUT}\)を小型化することができる)。また、出力コンデンサ\(C_{OUT}\)の発熱も抑えることができる。

デメリット

- 入力電流のリプルが大きい。

- 昇降圧コンバータよりも部品点数が多くなる。

補足

- 「Zeta」は日本語では「ジータ」と呼ぶことが多いです。

- Zetaコンバータはインダクタが2つ必要になりますが、2つのインダクタは同じ鉄心(コア)に巻くことができます。

- MOSFET\(Q\)はバイポーラトランジスタなど他のスイッチング素子でも使用可能です。

あわせて読みたい

SEPICコンバータの特徴や原理については下記の記事で説明しています。興味のある方は下記のリンクからぜひチェックをしてみてください。

-

SEPICコンバータとは?原理や計算式などを解説!

続きを見る

Zetaコンバータの回路構成

繰り替しになりますが、ZetaコンバータはInverse SEPIC(反転SEPIC)との別名があり、SEPICコンバータの入力と出力を反転させ、MOSFET\(Q\)とダイオード\(D\)を入れ替えた回路形態となっています。

SEPICコンバータは左から

インダクタ\(L_1\)

↓

スイッチング素子(MOSFET\(Q\))

↓

コンデンサ\(C\)

↓

インダクタ\(L_2\)

↓

スイッチング素子(ダイオード\(D\))

の順番になっており、

Zetaコンバータは右から

インダクタ\(L_2\)

↓

スイッチング素子(ダイオード\(D\))

↓

コンデンサ\(C\)

↓

インダクタ\(L_1\)

↓

スイッチング素子(MOSFET\(Q\))

の順番になっています。

Zetaコンバータの動作原理

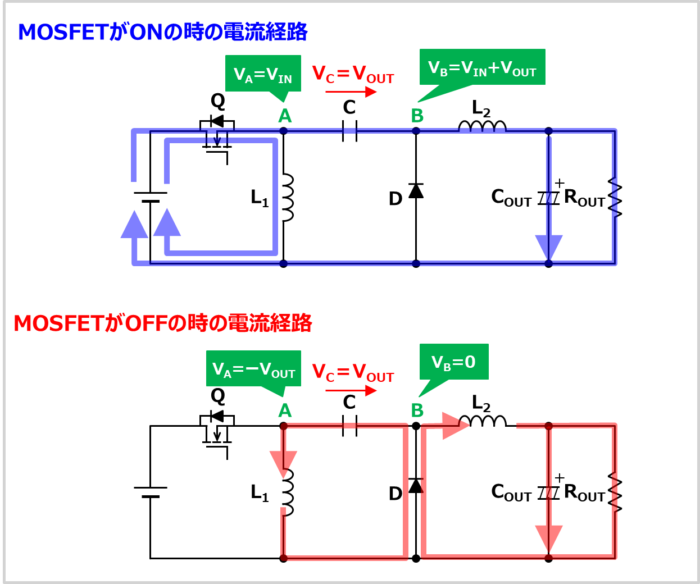

ではこれから、Zetaコンバータの動作原理について説明します。MOSFET\(Q\)が『ONの時』と『OFFの時』に分けて考えます。

MOSFET\(Q\)がONの時

MOSFET\(Q\)がONの時、『入力電圧\(V_{IN}\)→MOSFET\(Q\)→インダクタ\(L_1\)』の経路で電流が流れます。

また、コンデンサ\(C\)に蓄えられている電荷が放電するため、『入力電圧\(V_{IN}\)→MOSFET\(Q\)→コンデンサ\(C\)→インダクタ\(L_2\)→出力部(出力コンデンサ\(C_{OUT}\)+負荷抵抗\(R_{OUT}\))』の経路でも電流が流れています。

この期間では、インダクタ\(L_1\)および\(L_2\)に流れる電流が増加しており、この電流によりインダクタ\(L_1\)および\(L_2\)にエネルギーが蓄えられています。

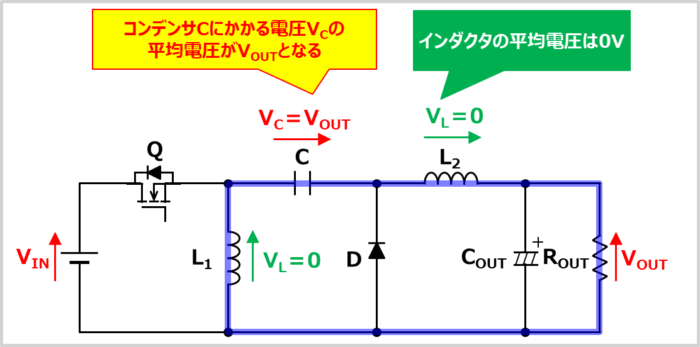

なお、コンデンサ\(C\)にかかる電圧\(V_C\)は「\(V_{OUT}\)」となるため、MOSFET\(Q\)のONによりA点の電圧\(V_A\)が「\(V_{IN}\)」になると、B点の電圧\(V_B\)は「\(V_{IN}+V_{OUT}\)」となります。

補足

- 定常状態においては、インダクタにかかる平均電圧は0Vなので、コンデンサ\(C\)にかかる電圧\(V_C\)の平均値が「\(V_{OUT}\)」となります。したがって、MOSFET\(Q\)のONによりA点の電圧\(V_A\)が「\(V_{IN}\)」になると、B点の電圧\(V_B\)は「\(V_{IN}+V_{OUT}\)」となります。

あわせて読みたい

インダクタンス\(L{\mathrm{[H]}}\)のインダクタに流れている電流が\(I{\mathrm{[A]}}\)の時、インダクタに蓄えられているエネルギー\(U{\mathrm{[J]}}\)は次式で表されます。

\begin{eqnarray}

U=\frac{1}{2}LI^2{\mathrm{[J]}}

\end{eqnarray}

インダクタのエネルギー\(U{\mathrm{[J]}}\)については別途下記の記事で詳しく説明していますので、ご参考にしてください。

-

コイルに蓄えられるエネルギーの『式』と『求め方』について!

続きを見る

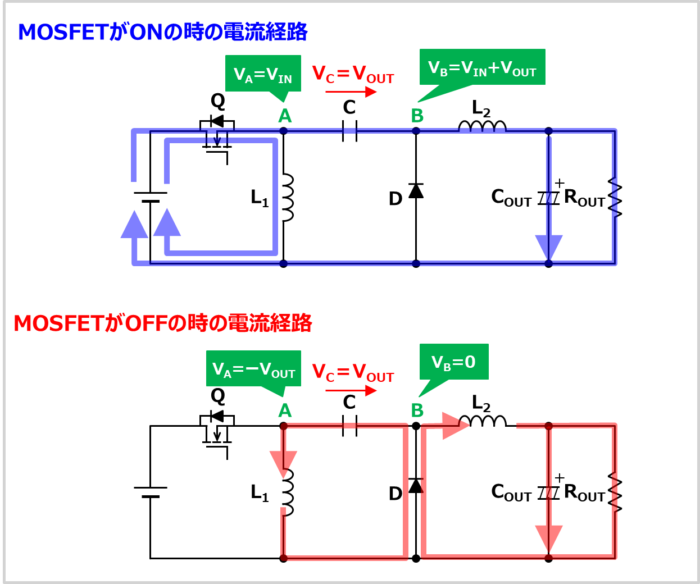

MOSFET\(Q\)がOFFの時

MOSFET\(Q\)がOFFになると、インダクタ\(L_1\)に蓄えられているエネルギーを放出して、電流を流し続けようとします。そのため、『インダクタ\(L_1\)→ダイオード\(D\)→コンデンサ\(C\)』の経路で電流が流れます。この電流により、コンデンサ\(C\)を充電しています。

また同様に、インダクタ\(L_2\)に蓄えられているエネルギーを放出して、電流を流し続けようとします。そのため、『インダクタ\(L_2\)→出力部(出力コンデンサ\(C_{OUT}\)+負荷抵抗\(R_{OUT}\))→ダイオード\(D\)』の経路でも電流が流れています。

なお、ダイオード\(D\)の順方向電圧降下\(V_F\)を無視すると、MOSFET\(Q\)がOFFの期間はB点の電圧\(V_B\)が0Vに引き下げられます。そのため、A点の電圧\(V_A\)は「\(-V_{OUT}\)」となります。

Zetaコンバータの出力電圧の式

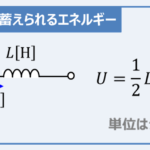

Zetaコンバータの出力電圧\(V_{OUT}\)は次式となります。

V_{OUT}=\frac{D}{1-D}V_{IN}\tag{1}

\end{eqnarray}

上式において、オンデューティ比\(D\)はMOSFET\(Q\)の1周期\(T\)におけるオン期間\(T_{ON}\)の割合なので、次式で表されます。

\begin{eqnarray}

D=\frac{T_{ON}}{T}=\frac{T_{ON}}{T_{ON}+T_{OFF}}=T_{ON}×f_{SW}\tag{2}

\end{eqnarray}

(2)式において、\(f_{SW}\)はMOSFET\(Q\)のスイッチング周波数です。(2)式から分かるように、オンデューティ比\(D\)は1より小さい値となります。

また、オンデューティ比\(D\)を0~1に変化させた時の\(\displaystyle\frac{V_{OUT}}{V_{IN}}\)のグラフを上図に示しています。

オンデューティ比\(D\)が0.5より大きい時は\(\displaystyle\frac{V_{OUT}}{V_{IN}}\)が1より大きく(\(V_{OUT}{>}V_{IN}\))、オンデューティ比\(D\)が0.5より小さい時は\(\displaystyle\frac{V_{OUT}}{V_{IN}}\)が1より小さく(\(V_{OUT}{<}V_{IN}\))なるため、昇降圧できることが式から分かります。

例えば、オンデューティ比\(D\)が0.6の場合と0.4の場合、出力電圧\(V_{OUT}\)は次式で表されます。

\begin{eqnarray}

V_{OUT}&=&\frac{D}{1-D}V_{IN}=\frac{0.6}{1-0.6}V_{IN}=\frac{3}{2}V_{IN}\tag{3}\\

\\

V_{OUT}&=&\frac{D}{1-D}V_{IN}=\frac{0.4}{1-0.4}V_{IN}=\frac{2}{3}V_{IN}\tag{4}

\end{eqnarray}

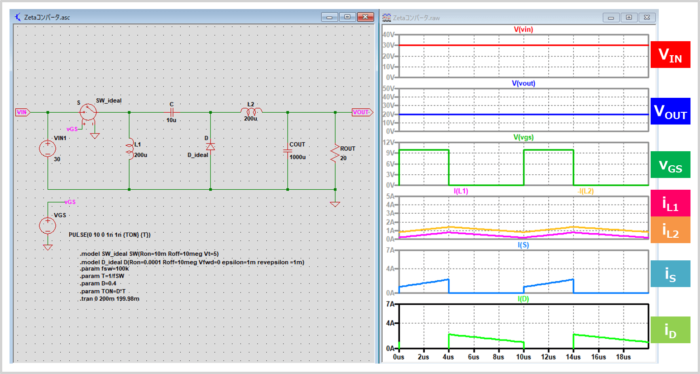

Zetaコンバータのシミュレーション

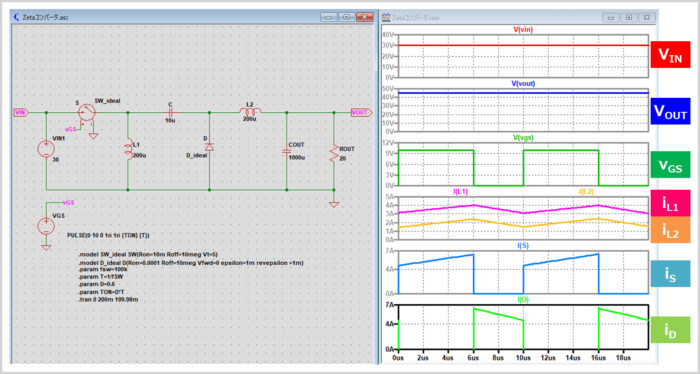

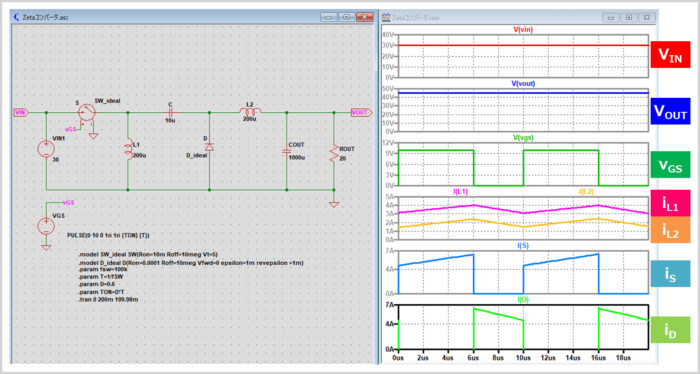

ZetaコンバータをLTspiceでシミュレーションした時の結果を上図に示しています。

上図の右側に示している波形は上から

- 入力電圧\(V_{IN}\)

- 出力電圧\(V_{OUT}\)

- スイッチ\(S\)の駆動信号\(v_{GS}\)

- インダクタ\(L_1,L_2\)に流れる電流\(i_{L1},i_{L2}\)

- スイッチ\(S\)に流れる電流\(i_S\)

- ダイオード\(D\)に流れる電流\(i_D\)

となっています。

MOSFET\(Q\)やダイオード\(D\)の損失を無視するために、シミュレーション回路ではMOSFET\(Q\)は理想スイッチ、ダイオード\(D\)は理想ダイオードを用いています。

また、入力電圧\(V_{IN}\)は30V、理想スイッチ\(S\)のオンデューティ比\(D\)は0.6にしています。そのため、出力電圧\(V_{OUT}\)は(1)式より

\begin{eqnarray}

V_{OUT}&=&\frac{D}{1-D}V_{IN}=\frac{0.6}{1-0.6}×30=45{\mathrm{[V]}}

\end{eqnarray}

となります。シミュレーション結果でも、出力電圧\(V_{OUT}\)が45Vとなり、昇圧動作をしていることが確認できます。

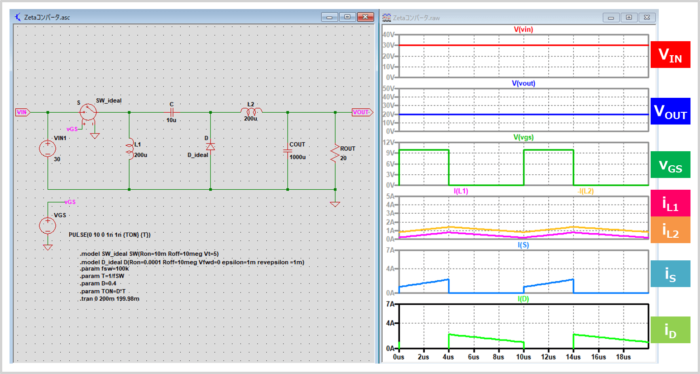

次に、オンデューティ比\(D\)を0.5より小さくした時に、降圧動作をしているかを確認してみましょう。理想スイッチ\(S\)のオンデューティ比\(D\)を0.4にした時のシミュレーション結果を下図に示しています。この場合、出力電圧\(V_{OUT}\)は(1)式より

\begin{eqnarray}

V_{OUT}&=&\frac{D}{1-D}V_{IN}=\frac{0.4}{1-0.4}×30=20{\mathrm{[V]}}

\end{eqnarray}

となります。シミュレーション結果でも、出力電圧\(V_{OUT}\)が20Vとなり、降圧動作をしていることが確認できます。

あわせて読みたい

LTspiceで理想スイッチと理想ダイオードを作る方法については、下記の記事で説明してますので、ご参考になれば幸いです。

-

【LTspice】理想スイッチである『電圧制御スイッチ』の使い方

続きを見る

-

【LTspice】『理想ダイオード』の作成方法

続きを見る

まとめ

この記事では『Zetaコンバータ』について、以下の内容を説明しました。

- Zetaコンバータとは

- Zetaコンバータの原理・計算式・シミュレーション

お読み頂きありがとうございました。

当サイトでは電気に関する様々な情報を記載しています。当サイトの全記事一覧は以下のボタンから移動することができます。

また、下記に当サイトの人気記事を記載しています。ご参考になれば幸いです。