「UVLO回路をビヘイビア電源で作成する方法」及び「UVLO回路をネットリストで作成する方法」を説明します。UVLO回路のネットリストはLTspice上ではIC内部のスパイスモデルに記述されていることがあります。

ではこれから詳しく説明します。

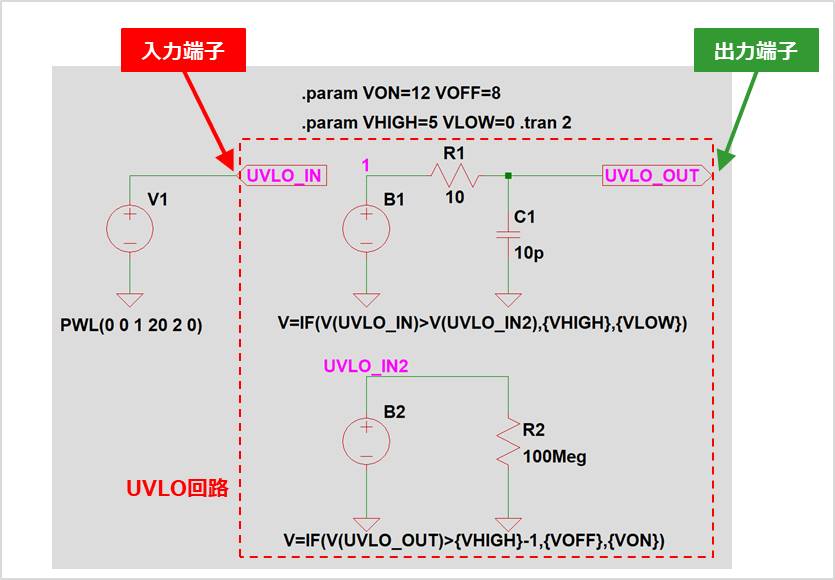

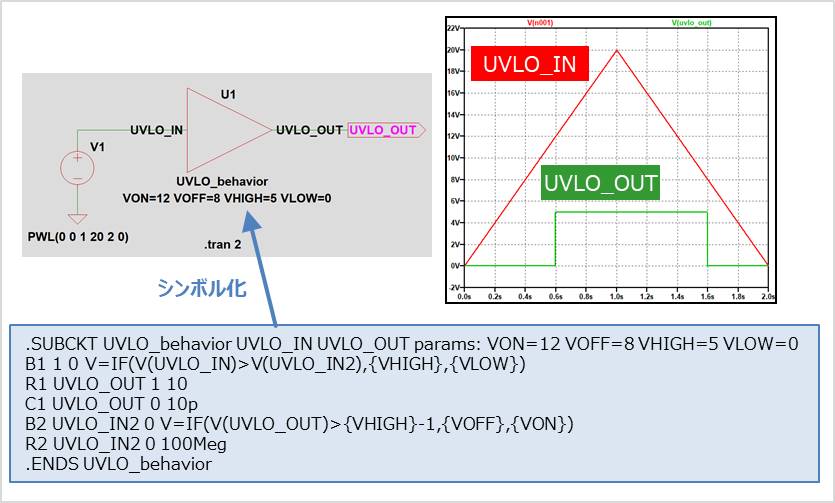

UVLO回路をビヘイビア電源で作成する方法

上図にビヘイビア電源を用いて作成したUVLO回路を示します。UVLO回路のブロックは赤色の点線で囲まれた箇所となっており、入力端子をUVLO_IN、出力端子をUVLO_OUTとしています。

UVLO回路の入力端子UVLO_INに電圧源V1を接続しています。電圧源V1の電圧はPWL(0 0 1 20 20)としています。この電圧源V1は0秒の時0V、1秒の時20V、2秒の時0Vと線形に変化します。

またUVLO回路では4つのパラメータを使用しています。以下に各パラメータを示します。

- VON

- VOFF

- VHIGH

- VLOW

UVLO回路のオン電圧。ここでは12Vとしました。

UVLO回路のオフ電圧。ここでは8Vとしました。

UVLO回路がオンした時の出力端子のハイ電圧。ここでは5Vとしました。

UVLO回路がオフした時の出力端子のロー電圧。ここでは0Vとしました。

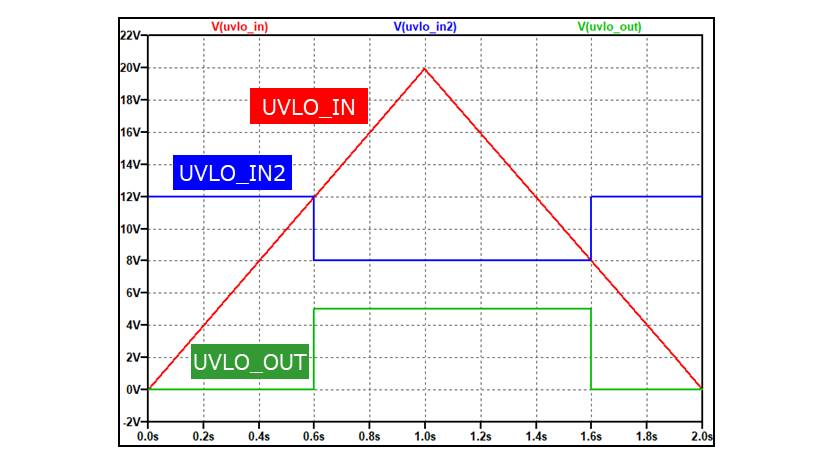

シミュレーション結果を以下に示します。後ほどこの回路の詳しい動作を説明しますが、「入力端子UVLO_INの電圧」が増加して、オン電圧VON(12V)になると、「出力端子UVLO_OUTの電圧」がハイ電圧VHIGH(5V)となっています。また、「入力端子UVLO_INの電圧」が減少して、オフ電圧VOFF(8V)になると、「出力端子UVLO_OUTの電圧」がロー電圧VLOW(0V)となっており、UVLO回路が作成できていることが確認できます。

ではこれから詳しい動作と原理について説明します。

UVLO回路の動作と原理

「入力端子UVLO_INの電圧」が0Vから12Vまで増加する時

「出力端子UVLO_OUTの電圧」は{VHIGH}-1より小さいため、ビヘイビア電源B2の以下の式

より、「ビヘイビア電源B2の出力端子UVLO_IN2の電圧」はVON(12V)となります。

また、「入力端子UVLO_INの電圧」は「入力端子UVLO_IN2の電圧」より小さいため、ビヘイビア電源B1の以下の式

より、「ビヘイビア電源B1の出力端子1の電圧」はVLOW(0V)となります。遅延回路R1C1を経由し、「出力端子UVLO_OUTの電圧」もVLOW(0V)となります。

「入力端子UVLO_INの電圧」が12V以上の時

「入力端子UVLO_INの電圧」は「入力端子UVLO_IN2の電圧」より大きいため、ビヘイビア電源B1の以下の式

より、「ビヘイビア電源B1の出力端子1の電圧」はVHIGH(5V)となります。遅延回路R1C1を経由し、「出力端子UVLO_OUTの電圧」もVHIGH(5V)となります。

その結果、「出力端子UVLO_OUTの電圧」は{VHIGH}-1より大きくなり、ビヘイビア電源B2の以下の式

より、「ビヘイビア電源B2の出力端子UVLO_IN2の電圧」はVOFF(8V)となります。

ここでのポイントは、「ビヘイビア電源B2の出力端子UVLO_IN2の電圧」が以下のように変化することです。これによりUVLO回路の動作を実現することができます。

- 「出力端子UVLO_OUTの電圧」がVLOW(0V)の時

- 「出力端子UVLO_OUTの電圧」がVHIGH(5V)の時

「ビヘイビア電源B2の出力端子UVLO_IN2の電圧」はVON(12V)。

「ビヘイビア電源B2の出力端子UVLO_IN2の電圧」はVOFF(8V)。

「入力端子UVLO_INの電圧」が減少し、8V以下になる時

「出力端子UVLO_OUTの電圧」は{VHIGH}-1より大きくなり、ビヘイビア電源B2の以下の式

より、「ビヘイビア電源B2の出力端子UVLO_IN2の電圧」はVOFF(8V)となります。

また、「入力端子UVLO_INの電圧」は「入力端子UVLO_IN2の電圧」より小さいため、ビヘイビア電源B1の以下の式

より、「ビヘイビア電源B1の出力端子1の電圧」はVLOW(0V)となります。遅延回路R1C1を経由し、「出力端子UVLO_OUTの電圧」もVLOW(0V)となります。

UVLO回路をネットリストで作成する方法

ビヘイビア電源で作成したUVLO回路をネットリストで表すと以下のようになります。

.SUBCKT UVLO_behavior UVLO_IN UVLO_OUT params: VON=12 VOFF=8 VHIGH=5 VLOW=0

B1 1 0 V=IF(V(UVLO_IN)>V(UVLO_IN2),{VHIGH},{VLOW})

R1 UVLO_OUT 1 10

C1 UVLO_OUT 0 10p

B2 UVLO_IN2 0 V=IF(V(UVLO_OUT)>{VHIGH}-1,{VOFF},{VON})

R2 UVLO_IN2 0 100Meg

.ENDS UVLO_behavior

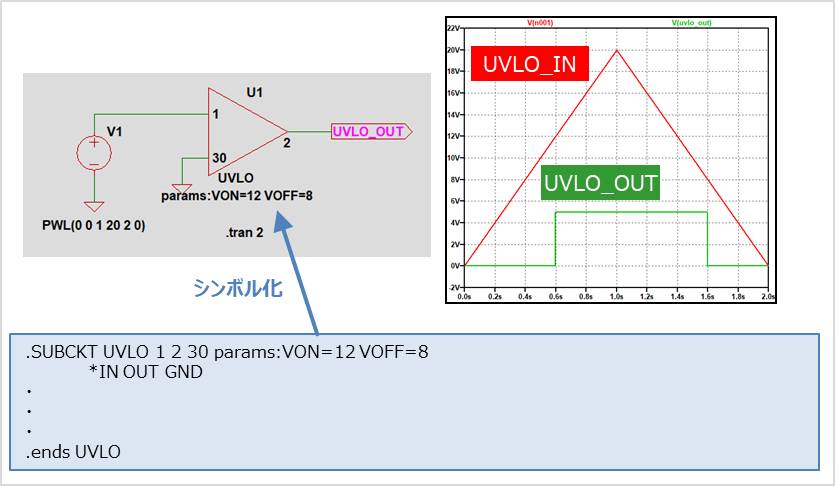

このネットリストをシンボル化したものを以下に示します。シミュレーション結果が「ビヘイビア電源で作成したUVLO回路」と同じであることが確認できます。

ICのモデル内部で記述されているUVLO回路の一例

少し難しくなりますが、ICのスパイスモデル等を見ると、UVLO回路のネットリストが記述されていることがあります。一般的にはPspiceで記述されています。以下にUVLO回路の一例を示します。

.SUBCKT UVLO 1 2 30 params:VON=12 VOFF=8

*IN OUT GND

X1 1 3 1 30 SWhyste params:RON=1 ROFF=1E6 VT={((VON-VOFF)/2)+VOFF} VH={(VON-VOFF)/2}

RUV 3 30 100K

E1 4 0 Value = {IF(V(3,30)>5,5,0)}

RD 4 2 100

CD 2 0 100P

.ENDS UVLO

.subckt SWhyste NodeMinus NodePlus Plus Minus PARAMS: RON=1 ROFF=1MEG VT=5 VH=2

S5 NodePlus NodeMinus 8 0 smoothSW

EBcrtl 8 0 Value = { IF ( V(plus)-V(minus) > V(ref), 1, 0 ) }

EBref ref1 0 Value = { IF ( V(8) > 0.5, {VT-VH}, {VT+VH} ) }

Rdel ref1 ref 100

Cdel ref 0 100p IC={VT+VH}

Rconv1 8 0 10Meg

Rconv2 plus 0 10Meg

Rconv3 minus 0 10Meg

.model smoothSW VSWITCH (RON={RON} ROFF={ROFF} VON=1 VOFF=0)

.ends SWhyste

上記のネットリストをLTspiceでの記述に変換すると以下のようになります。

.SUBCKT UVLO 1 2 30 params:VON=12 VOFF=8

*IN OUT GND

X1 1 3 1 30 SWhyste params:RON=1 ROFF=1E6 VT={((VON-VOFF)/2)+VOFF} VH={(VON-VOFF)/2}

RUV 3 30 100K

BE1 4 0 V= IF(V(3,30)>5,5,0)

RD 4 2 100

CD 2 0 100P

.ENDS UVLO

.SUBCKT SWhyste SW_Minus SW_Plus IN_Plus IN_Minus PARAMS: RON=1 ROFF=1MEG VT=5 VH=2

S1 SW_Plus SW_Minus NC1 0 SmoothSW

B_Crtl NC1 0 V = IF ( V(IN_Plus)-V(IN_Minus) > V(Ref), 2, 0 )

B_Ref Ref1 0 V = IF ( V(NC1) > 0.5, {VT-VH}, {VT+VH} )

Rdel Ref1 Ref 100

Cdel Ref 0 100p IC={VT+VH}

Rconv1 NC1 0 10Meg

Rconv2 IN_Plus 0 10Meg

Rconv3 IN_Minus 0 10Meg

.model SmoothSW SW(RON={RON} ROFF={ROFF} VT=0.5 VH=0.5)

.ends SWhyste

このネットリストをシンボル化したものを以下に示します。シミュレーション結果が「ビヘイビア電源で作成したUVLO回路」と同じであることが確認できます。

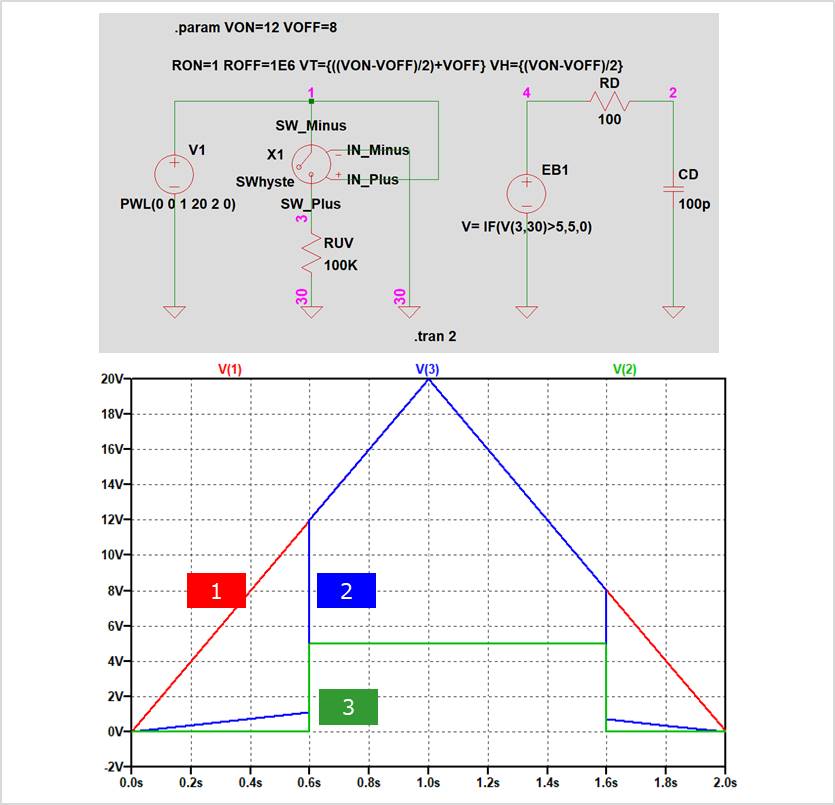

ICのモデル内部で記述されているUVLO回路を描く

先ほどはビヘイビア電源を用いてUVLO回路を作成しましたが、ICのモデル内部で記述されているUVLO回路はヒステリシススイッチSWhysteを用いてUVLO回路を作成しています。詳しい説明は割愛しますが、軽く動作を説明します。

入力電圧V1の電圧がヒステリシススイッチSWhysteのオン電圧VON(12V)を超えると、ヒステリシススイッチSWhysteがオンします。その結果、入力電圧V1の電圧が3番端子に印可され、V(3,30)が入力電圧V1と等しくなります。

「3番端子の電圧V(3,30)」は5V以上あるため、ビヘイビア電源EB1の出力が5Vとなります。

一方、入力電圧V1の電圧がヒステリシススイッチSWhysteのオフ電圧VOFF(8V)を下回ると、ヒステリシススイッチSWhysteがオフします。その結果、「3番端子の電圧V(3,30)」が低下し5V以下となります。「3番端子の電圧V(3,30)」はヒステリシススイッチのオフ抵抗と抵抗RUVによって決まります。「3番端子の電圧V(3,30)」は5V以下であるため、ビヘイビア電源EB1の出力が0Vとなります。

シミュレーション結果が「ビヘイビア電源で作成したUVLO回路」と同じであることが確認できます。