LTspiceにはSRフリップフロップの論理回路があります。

SRフリップフロップはデジタル回路では有名な回路であり、LTspice上では主にICのモデル内に使用されています。

この記事では

- SRフリップフロップの作成方法・使い方

- ビヘイビア電源によるSRフリップフロップの作成方法

を説明します。

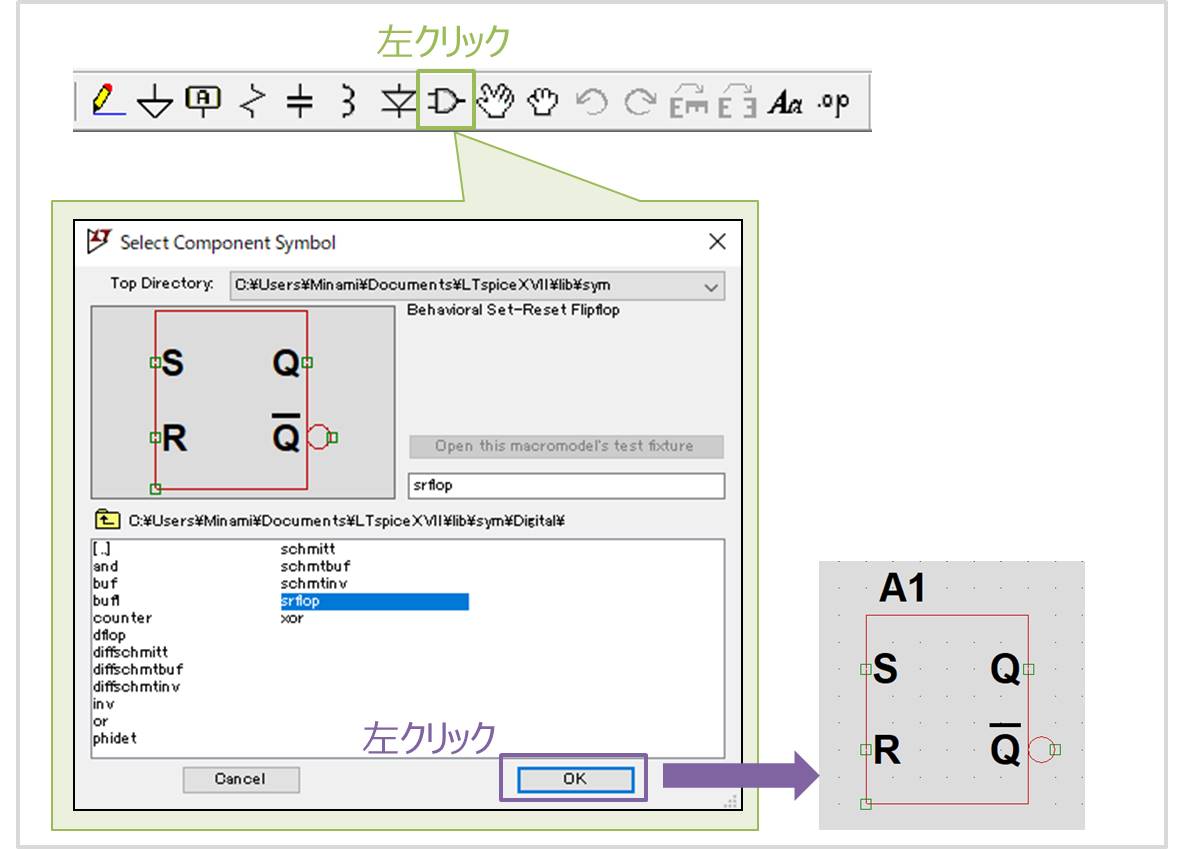

SRフリップフロップの出し方

- LTspiceを開いた後、メニューバーでcomponentボタンを押します。

- 「Select Component Symbol」が開くので、srflopを選択し、OKボタンを押します。

- SRフリップフロップ(SRFLOP)が回路図上に表示されます。

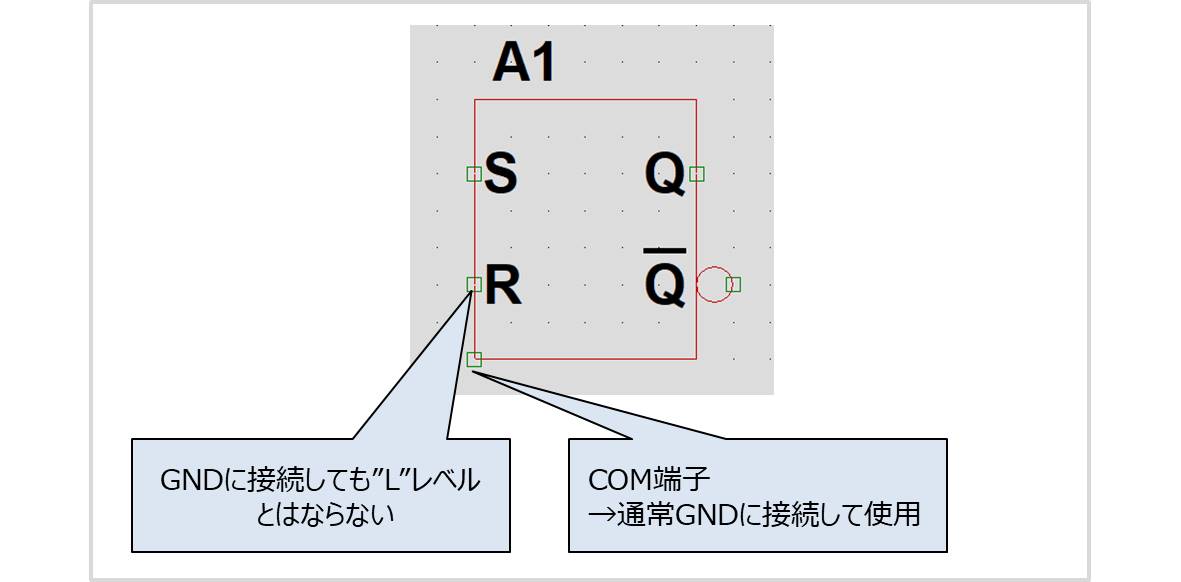

SRフリップフロップのポイント

- SRフリップフロップの左下角にある丸はCOM端子となっています。このCOM端子は通常GNDに接続して使用します。また、入力(S,R)と出力(Q,Q反転)の端子で使用しないものはCOM端子に接続すると、シミュレーション時間を短縮することができます。

- COM端子やGNDを入力端子(S,R)に接続しても、入力の論理レベルは”L”となりません。”L”にするためには、0V(厳密にはVt以下)の電圧源を入力に接続する必要があります。

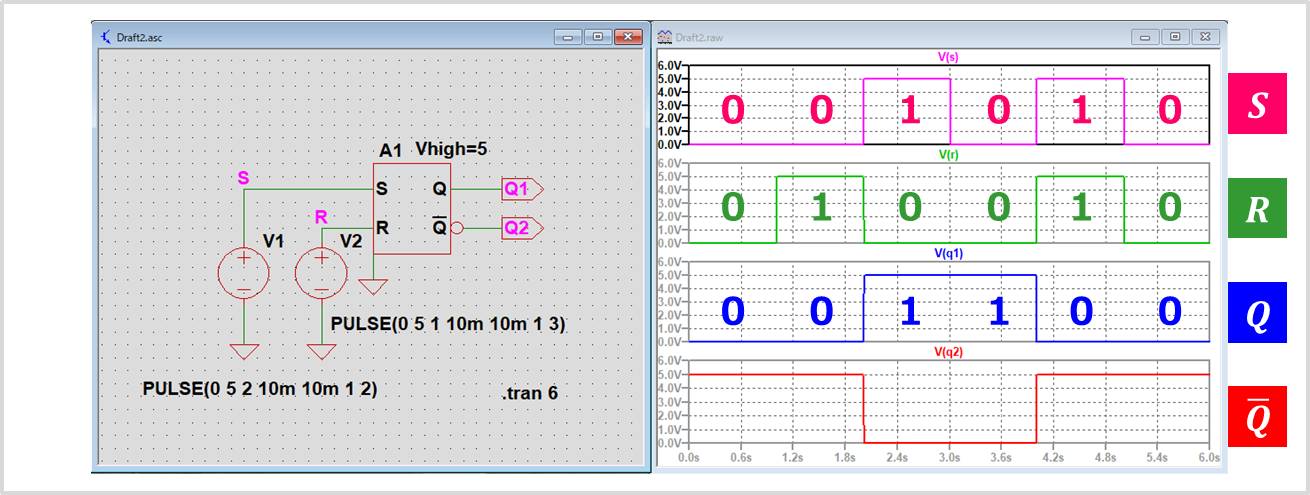

SRフリップフロップ回路のシミュレーション例

実際にSRフリップフロップを使用してみましょう。上図のシミュレーションでは入力端子Sにパルス電圧V1、入力端子Rにパルス電圧V2を接続した時の出力端子の電圧を観測しています。上の右がシミュレーション結果となっており、ピンクがS、緑がR、青が出力Q、赤が出力Qの反転電圧となっています。

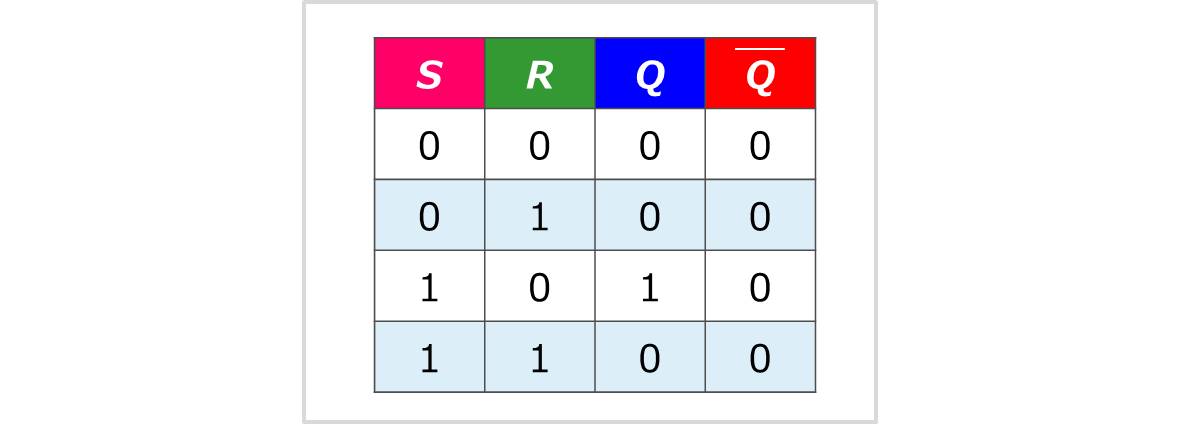

入力(S,R)と出力(Q,Q反転)の関係は下表のようになり、SRフリップフロップ回路となっていることが確認できます(SRフリップフロップについて後日記載します)。

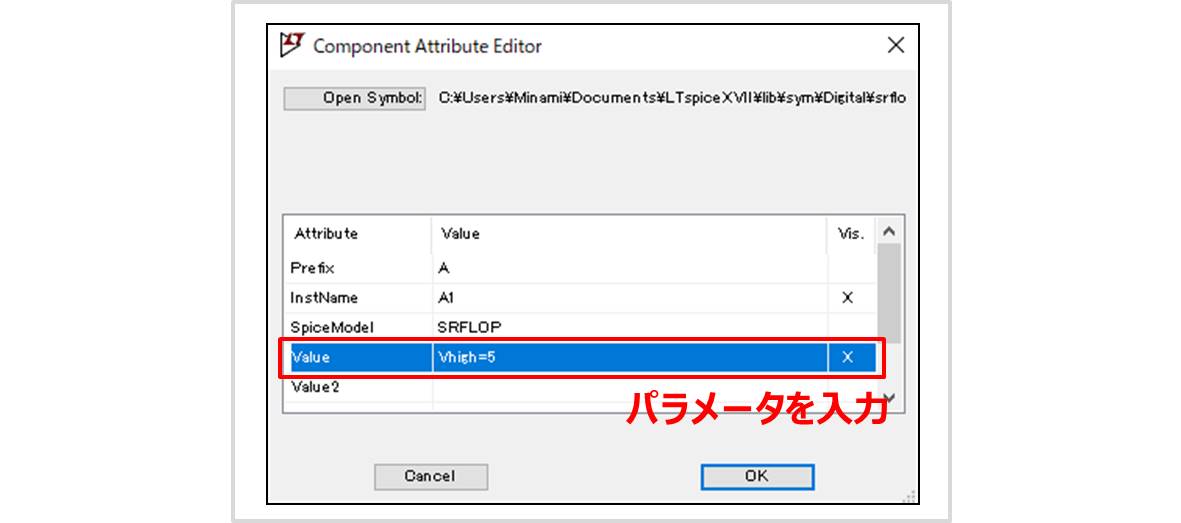

また、SRフリップフロップはパラメータを設定することができます。SRフリップフロップにある「Vhigh=5」はパラメータです。パラメータはコントロール(Ctrl)を押しながら、部品を右クリックした際に出てくるComponent Attribute Editorメニューの「Value」にパラメータを入力することで設定できます。

「Vhigh」は出力の”H”レベルとなっており、デフォルトでは1Vになります。今回は入力端子に印可される電圧が5Vなので、「Vhigh=5V」としています。「Vhigh」は入力の電圧より低くしないとSRフリップフロップが正常に動作しません。

「Vhigh」以外にもパラメータがあります。そのパラメータを以下に示します。

| パラメータ | デフォルト値 | 意味 |

| Vhigh | 1 | Logic high level(論理"H"レベル) |

| Vlow | 0 | Logic low level(論理"L"レベル) |

| Trise | 0 | Rise time(立ち上がり時間) |

| Vfall | Trise | Fall time(立ち下がり時間) |

| Tau | 0 | Output RC time constant(RC時定数) |

| Cout | 0 | Output capacitance(出力キャパシタンス) |

| Rout | 1 | Output impedance(出力インピーダンス) |

| Rhigh | Rout | Logic high level impedance(論理"H"レベルインピーダンス) |

| Rlow | Rout | Logic low level impedance(論理"L"レベルインピーダンス) |

| Td | 0 | Propagation delay(伝搬遅延) |

| Ref | 0.5*(Vhigh+Vlow) | Input Logic threshold |

| Vt | 0.5*(Vhigh+Vlow) | Schmitt input trip point(閾値電圧) |

| Vh | 0.1 | Schmitt input hysteresis(ヒステリシス電圧) |

ビヘイビア電源でSRフリップフロップを作成する方法

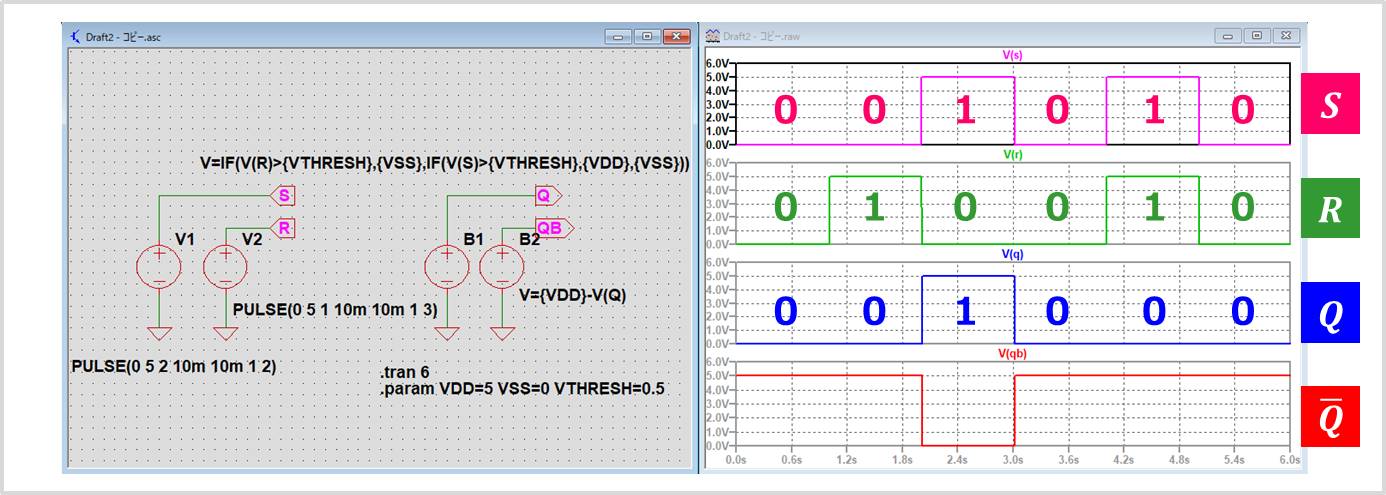

ビヘイビア電源を用いてもSRフリップフロップを作成することができます。上図のシミュレーションでは入力端子Sにパルス電圧V1、入力端子Rにパルス電圧V2を接続した時の出力端子の電圧を観測しています。上の右がシミュレーション結果となっており、ピンクがS、緑がR、青が出力Q、赤が出力Qの反転電圧となっています。

ビヘイビア電源B1の式は以下のように記述します。

これはリセットRが{VTHRESH}より大きい時は{VSS}となり、リセットRが{VTHRESH}より小さいとき&セットSが{VTHRESH}より大きい時に{VDD}となるようにしています。

入力(S,R)と出力(Q,Q反転)の関係は下表のようになり、SRフリップフロップ回路となっていることが確認できます。

LTspiceと異なるのは、リセットRに信号が入ると必ず出力Qが0になる点です。そのため、厳密にはSRフリップフロップではないのですが、ICもモデル内にはこのSRフリップフロップ回路が使用されていることが多いです。

上の回路をネットリストで記述すると以下のようになります。

B1 Q 0 V=IF(V(R)>{VTHRESH},{VSS},IF(V(S)>{VTHRESH},{VDD},{VSS}))

B2 QB 0 V={VDD}-V(Q)

.ENDS SRLATCH