この記事ではロードスイッチの回路構成や動作について図を用いて分かりやすく説明しています。

ロードスイッチとは

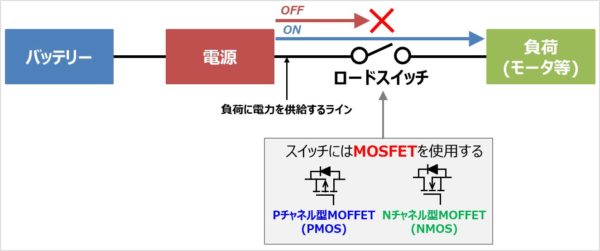

ロードスイッチとは、負荷(モータ、AV機器、ポータブル機器等)に電力を供給するラインに対して、ON/OFFを行うスイッチのことです。

スイッチがONの時に負荷に電力を供給し、スイッチがOFFの時に負荷への電力供給を遮断します。

このスイッチにはMOSFETが使用されます。そのため、MOSFETの代表的な応用分野の1つがロードスイッチということになります。

ロードスイッチに用いるMOSFETは一般的にはPチャネル型MOFFET(PMOS)が使用されますが、Nチャネル型MOFFET(NMOS)が使用されることもあります。

補足

ロードスイッチは電源側をスイッチするため、ハイサイドスイッチとも呼ばれています。

ロードスイッチの回路構成

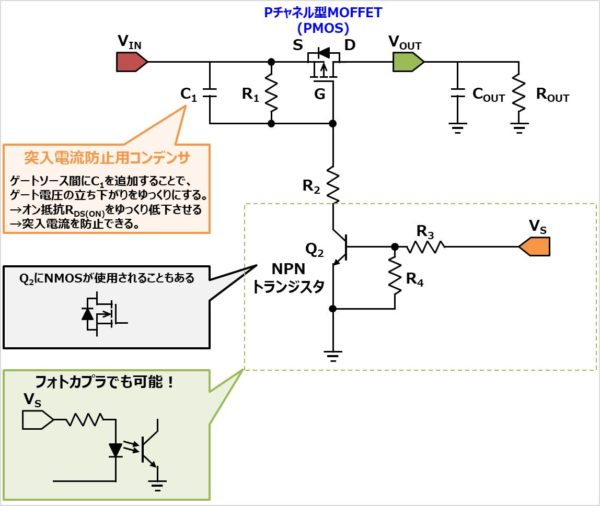

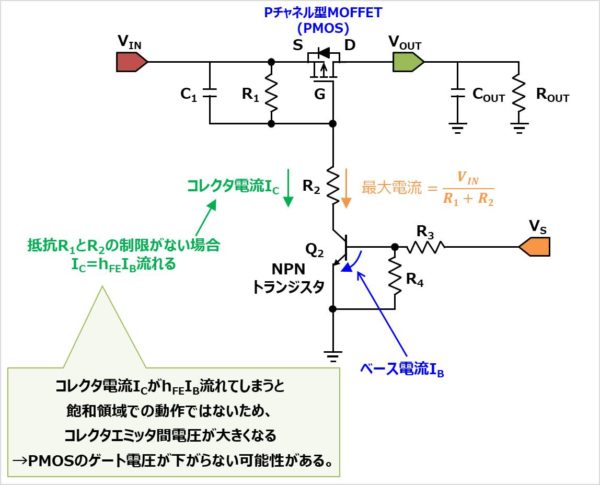

Pチャネル型MOFFETを使用したロードスイッチ

ロードスイッチにPチャネル型MOFFETを用いた時の回路構成は上図のようになります。

Pチャネル型MOFFETのソース(S)を入力側、ドレイン(D)を出力側に配置します。

これは、Pチャネル型MOFFETと並列についている逆流防止ダイオードの向きをカソードを入力側、アノードを出力側にするためです。このようにすることで、Pチャネル型MOFFETがOFFの時に入力側から出力側に電流が流れるのを防止します。

また、Pチャネル型MOFFETのゲートソース間にはコンデンサC1と抵抗R1を接続します。コンデンサC1と抵抗R1の役割を以下に示します。

コンデンサC1の役割

コンデンサC1は突入電流防止用のコンデンサです。

ゲート電圧VGの立ち下がりをゆっくりにし、Pチャネル型MOFFETのオン抵抗RDS(ON)をゆっくり低下させることで、突入電流を防止しています。

抵抗R1の役割

抵抗R1はトランジスタQ2がONした時に、抵抗R1と抵抗R2で分圧するための抵抗です。この分圧を調整してPチャネル型MOFFETのゲートソース間電圧を決定させます。

また、Pチャネル型MOFFETのゲートにはトランジスタQ2を接続します。トランジスタQ2の役割を以下に示します。

トランジスタQ2の役割

トランジスタQ2はPチャネル型MOFFETを制御するためのトランジスタです。

トランジスタQ2がOFFの時、Pチャネル型MOFFETのゲートソース間電圧がゼロとなり、Pチャネル型MOFFETがOFFします。

トランジスタQ2がONの時、抵抗R1と抵抗R2によりPチャネル型MOFFETのゲートソース間に電圧が印加され、Pチャネル型MOFFETがONします。この時ゲートソース間電圧VGSは次式となります。

\begin{eqnarray}

V_{GS}=\frac{R_{2}}{R_{1}+R_{2}}V_{IN}-V_{IN}

\end{eqnarray}

補足

- トランジスタQ2にはNPNトランジスタやNチャネル型MOFFETが使用されます。また、Pチャネル型MOFFETを制御するためにフォトカプラを使用することもあります。

- 一般的にはロードスイッチはPチャネル型MOFFETを使用した構成が有名ですが、Pチャネル型MOFFETはNチャネル型MOFFETに比べて高く、メーカーも生産終了や販売終了することがNチャネル型MOFFETと比較して高くなっています。そのため、少し回路が複雑になりますが、ロードスイッチにNチャネル型MOFFETを用いている場合もあります。

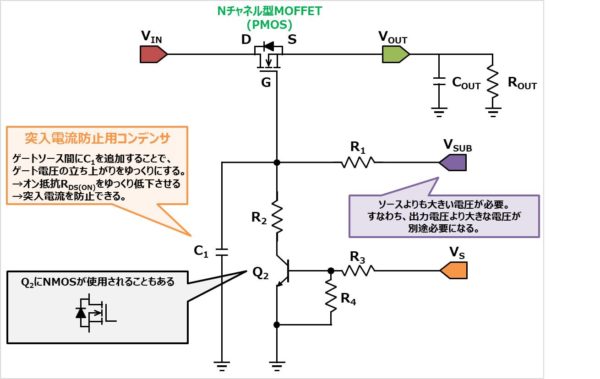

Nチャネル型MOFFETを使用したロードスイッチ

ロードスイッチにNチャネル型MOFFETを用いた時の回路構成は上図のようになります。

Nチャネル型MOFFETのソース(S)を出力側、ドレイン(D)を入力側に配置します。

これは、Nチャネル型MOFFETと並列についている逆流防止ダイオードの向きをカソードを入力側、アノードを出力側にするためです。このようにすることで、Nチャネル型MOFFETがOFFの時に入力側から出力側に電流が流れるのを防止します。

Nチャネル型MOFFETをONするためには、ゲートソース間電圧VGSが正になる必要があります。すなわち、ソースの電圧よりもゲートの電圧の方が高くなる必要があります。そのため、Nチャネル型MOFFETをONするために別途、出力電圧VOUTより高い電圧VSUBが必要になります。

また、Nチャネル型MOFFETのゲートにはコンデンサC1と抵抗R1を接続します。コンデンサC1と抵抗R1の役割を以下に示します。

コンデンサC1の役割

コンデンサC1は突入電流防止用のコンデンサです。

原理はPチャネル型MOFFETと同様で、ゲート電圧VGの立ち上がりをゆっくりにし、Nチャネル型MOFFETのオン抵抗RDS(ON)をゆっくり低下させることで、突入電流を防止しています。

抵抗R1の役割

抵抗R1はトランジスタQ2がONした時に、抵抗R1と抵抗R2で分圧するための抵抗です。

トランジスタQ2がONした時、電圧VSUBが抵抗R1と抵抗R2で分圧され、Nチャネル型MOFFETのゲートに印加されます。そのため、ソースの電圧よりもゲートの電圧の方が低くなり、Nチャネル型MOFFETがOFFします。

抵抗R1がない場合、トランジスタQ2がONしても、Nチャネル型MOFFETのゲート電圧が電圧VSUBと等しいため、Nチャネル型MOFFETをOFFすることができなくなります。

また、Nチャネル型MOFFETのゲートにはトランジスタQ2を接続します。トランジスタQ2の役割を以下に示します。

トランジスタQ2の役割

トランジスタQ2はNチャネル型MOFFETを制御するためのトランジスタです。

トランジスタQ2がONの時、電圧VSUBが抵抗R1と抵抗R2で分圧され、Nチャネル型MOFFETのゲートに印加されます。そのため、ソースの電圧よりもゲートの電圧の方が低くなり、Nチャネル型MOFFETがOFFします。

トランジスタQ2がOFFの時、出力電圧VOUTより高い電圧VSUBがNチャネル型MOFFETのゲートに印加されます。このゲートソース間電圧VGSがNチャネル型MOFFETの閾値電圧を超えるとONします。なお、ゲートソース間電圧VGSは次式となります。

\begin{eqnarray}

V_{GS}=V_{SUB}-V_{OUT}

\end{eqnarray}

ロードスイッチの動作

Pチャネル型MOFFETを使用したロードスイッチの動作

VSからHighレベルが出力された場合

- トランジスタQ2のベースに電圧を供給する電圧源VSがHighレベルの時、抵抗R3と抵抗R4を通りグラウンドに電流が流れます。

- トランジスタQ2のベースエミッタ間電圧が閾値電圧以上になると、トランジスタQ2のベースからエミッタにベース電流IBが流れます(その時、R4にも微小電流が流れています)。

- 通常、トランジスタQ2はこのベース電流IBのhFE倍(小電力用だと約100程度)のコレクタ電流ICをコレクタからエミッタに流します。しかし、実際には、抵抗R1と抵抗R2によって電流が制限され、『\(\displaystyle\frac{V_{IN}}{R_{1}+R_{2}}\)』以上のコレクタ電流ICを流すことができなくなります。トランジスタにとってより多くのコレクタ電流ICを流したくても流せない状態を、飽和と呼びます。トランジスタが飽和状態ではない場合、コレクタエミッタ間電圧VCEが大きくなります。

- トランジスタを飽和状態にするために、コレクタ電流ICが『\(\displaystyle\frac{V_{IN}}{R_{1}+R_{2}}\)』以上流れるようにベース電流IBを流す必要があります。式で表すと次式となります。

\begin{eqnarray}

\frac{V_{IN}}{R_1+R_2}{\;}{<}{\;}h_{FE}I_B{\;}{\Leftrightarrow}{\;}\frac{V_{IN}}{R_1+R_2}\frac{1}{h_{FE}}{\;}{<}{\;}I_B

\end{eqnarray}余裕をもって上式の2倍以上のベース電流IBを流すように抵抗R3の値を設計をします。

- トランジスタQ2がONすると、入力電圧VINからグランドに向かって電流が流れるルートができます。その結果、Pチャネル型MOFFETのゲートソース間電圧に電位差が生じて、Pチャネル型MOFFETがONします。

VSからLowレベルが出力された場合

- トランジスタQ2のベースに電圧を供給する電圧源VSがLowレベルの時、トランジスタQ2のベースからエミッタにベース電流IBが流れず、トランジスタQ2はOFFとなります。

- トランジスタQ2がOFFの場合、コレクタからエミッタにコレクタ電流ICが流れません。

- コレクタ電流ICが流れないので、コンデンサC1に蓄積されている電荷は抵抗R1によって消費され、Pチャネル型MOFFETのゲートソース間電圧VGSは徐々に低下していきます。その結果、Pチャネル型MOFFETがOFFとなります。

Nチャネル型MOFFETを使用したロードスイッチの動作

『Pチャネル型MOFFETを使用したロードスイッチの動作』での考え方と同じです。

- トランジスタQ2をONした場合、電圧源VSUBからグランドに向かって電流が流れるルートができます。その結果、Nチャネル型MOFFETがOFFします。

- トランジスタQ2をOFFした場合、Nチャネル型MOFFETのゲートに電圧VSUBが電圧が印可され、Nチャネル型MOFFETがONします。

まとめ

この記事ではロードスイッチについて、以下の内容を説明しました。

当記事のまとめ

- ロードスイッチとは

- ロードスイッチの回路構成

- ロードスイッチの動作

お読み頂きありがとうございました。

当サイトでは電気に関する様々な情報を記載しています。当サイトの全記事一覧には以下のボタンから移動することができます。