NPNトランジスタとPNPトランジスタの2つを使用したラッチ回路に関して、抵抗値の設計方法について説明します。その後、LTspiceを用いたシミュレーションでラッチ回路の動作確認をします。

ラッチ回路の『抵抗値』の設計方法

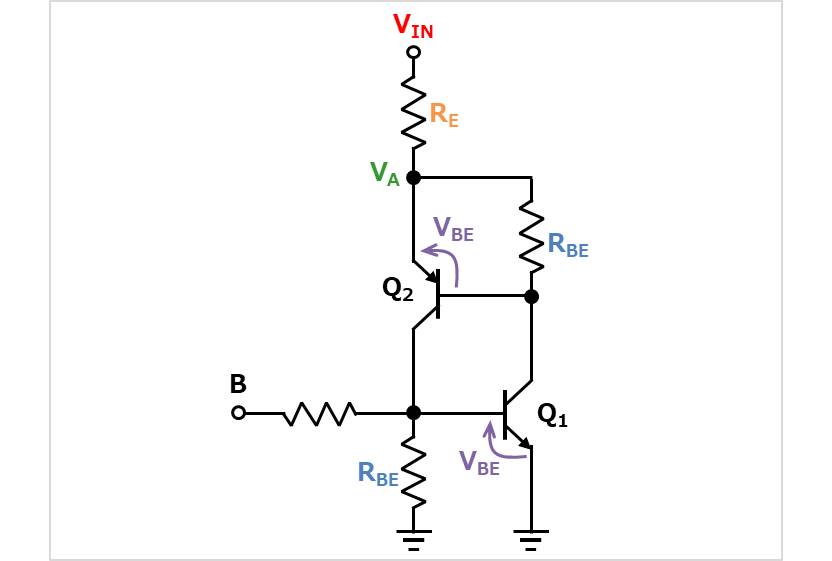

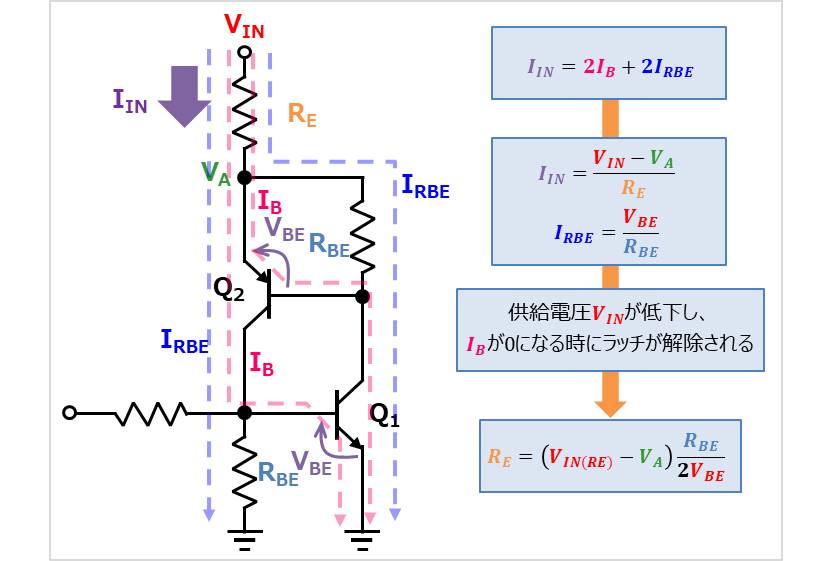

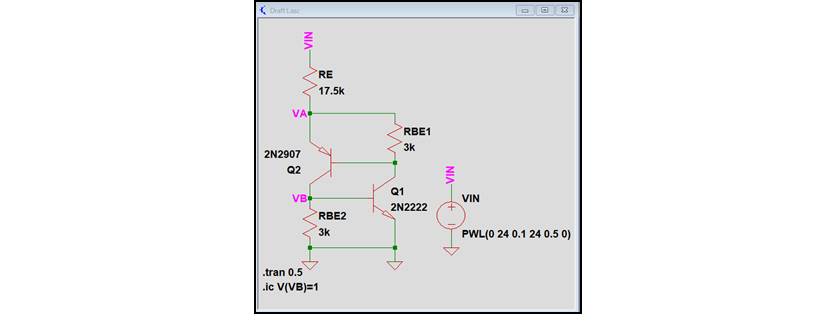

上図にラッチ回路を示します。ラッチ回路はノードBに電圧が印可される等によってNPNトランジスタ\(Q_1\)のベースに電流が流れると、NPNトランジスタ\(Q_1\)とPNPトランジスタ\(Q_2\)がオン状態を維持する回路です。

ラッチ回路への供給電圧\(V_{IN}\)を遮断し、PNPトランジスタ\(Q_2\)のエミッタに電流を流さなくすると、オン状態が解除(ラッチ解除)されます。

しかし、抵抗\(R_{E}\)の抵抗値が大きく、抵抗\(R_{BE}\)の抵抗値が小さい場合、供給電圧\(V_{IN}\)が少し下がるだけで、ラッチ解除してしまう場合があります。

今回は、ラッチが解除される電圧\(V_{IN(RE)}\)、抵抗\(R_{E}\)、抵抗\(R_{BE}\)の関係式を導出し、各抵抗の抵抗値を設計する方法を説明します。

なお、ラッチ回路の動作等については以下の記事に記載しています。 続きを見る

ラッチ回路(自己保持回路)とは?トランジスタを使用した回路と動作について

ラッチが解除される電圧\(V_{IN(RE)}\)、抵抗\(R_{E}\)及び抵抗\(R_{BE}\)の抵抗値の関係

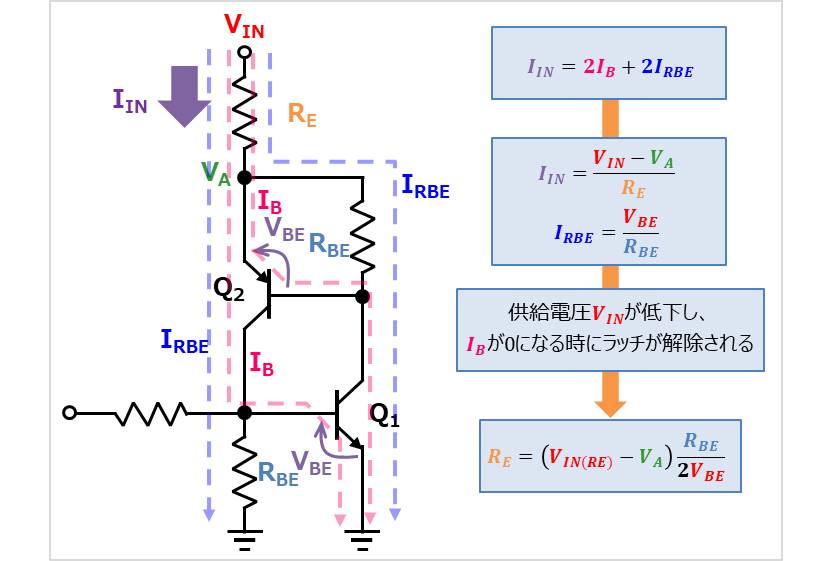

抵抗\(R_{E}\)に流れる電流を\(I_{IN}\)、各トランジスタのベースに流れる電流を\(I_{B}\)、抵抗\(R_{BE}\)に流れる電流を\(I_{RBE}\)とすると、キルヒホッフの法則より以下の式が成り立ちます。

\begin{eqnarray}

I_{IN}=2I_{B}+2I_{RBE}\tag{1}

\end{eqnarray}

ここで電流\(I_{IN}\)及び電流\(I_{RBE}\)はオームの法則より以下の式が成り立ちます。

\begin{eqnarray}

I_{IN}&=& \frac{V_{IN}-V_A}{R_E}\tag{2}\\

I_{RBE}&=&\frac{V_{BE}}{R_{BE}}\tag{3}

\end{eqnarray}

(2)式と(3)式を(1)式に代入すると以下の式となります。

\begin{eqnarray}

\frac{V_{IN}-V_A}{R_E}=2I_{B}+2\frac{V_{BE}}{R_{BE}}\tag{4}

\end{eqnarray}

供給電圧\(V_{IN}\)が低下し、ベース電流\(I_{B}\)が0Aになる時、ラッチが解除されます。この時の供給電圧を\(V_{IN(RE)}\)とすると、以下の式が成り立ちます。

\frac{V_{IN(RE)}-V_A}{R_E}=0+2\frac{V_{BE}}{R_{BE}}\\

{\Leftrightarrow}{R_E}=(V_{IN(RE)}-V_A)×\frac{R_{BE}}{2V_{BE}}\tag{5}

\end{eqnarray}

ラッチ回路の『抵抗値』の設計値導出

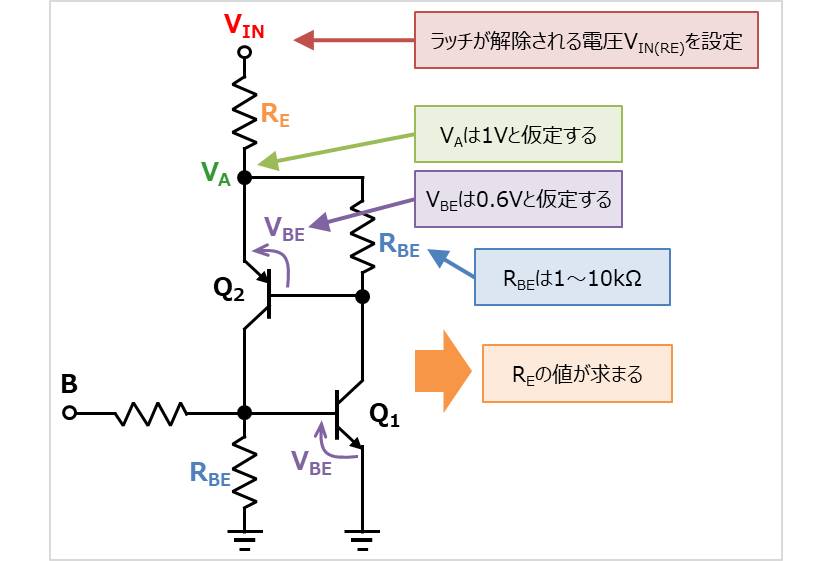

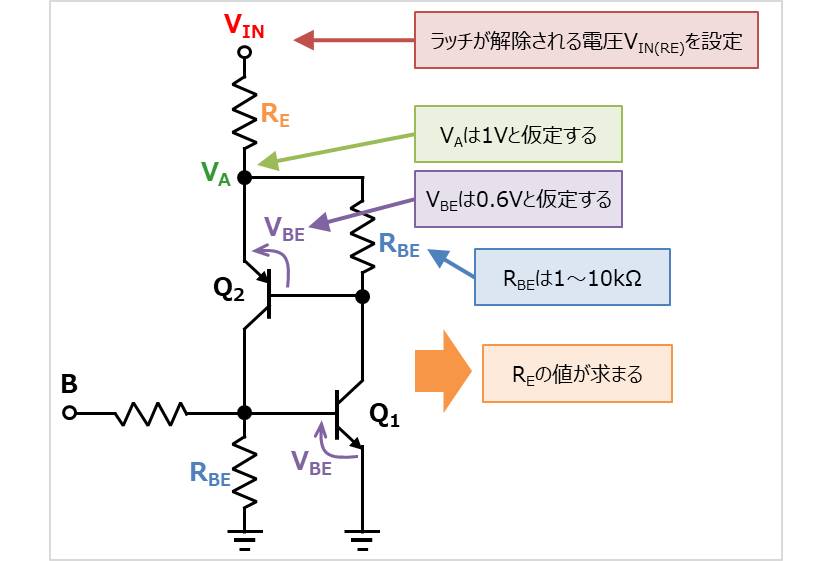

ラッチ回路は以下のように設計を行います。

- ラッチが解除される電圧\(V_{IN(RE)}\)を設定する

- 電圧\(V_{A}\)を1Vと仮定する

- 抵抗\(R_{BE}\)は1~10kΩとする

今回は一例として8Vとしました。

電圧\(V_{A}\)はラッチ回路動作時はトランジスタ\(Q_1\)のベースエミッタ間電圧\(V_{BE}\)とトランジスタ\(Q_2\)のコレクタエミッタ間電圧\(V_{CE}\)の和となります。ベースエミッタ間電圧\(V_{BE}\)は約0.6Vであり、コレクタエミッタ間電圧\(V_{CE}\)は約0.3Vなので、\(V_{A}\)を1Vとしました。

ネットや参考書等でラッチ回路を見ると、ベースエミッタ間抵抗は1~10kΩの範囲にしているのが多いです。今回は一例として3kΩとしました。

上記の値を(5)式に代入すると、抵抗\(R_{E}\)の値は

\begin{eqnarray}

{R_E}&=&(V_{IN(RE)}-V_A)×\frac{R_{BE}}{2V_{BE}}\\

&=& (8A-1A)×\frac{3kΩ}{2×0.6V}\\

&=&17.5kΩ

\end{eqnarray}

となります。

シミュレーションで確認

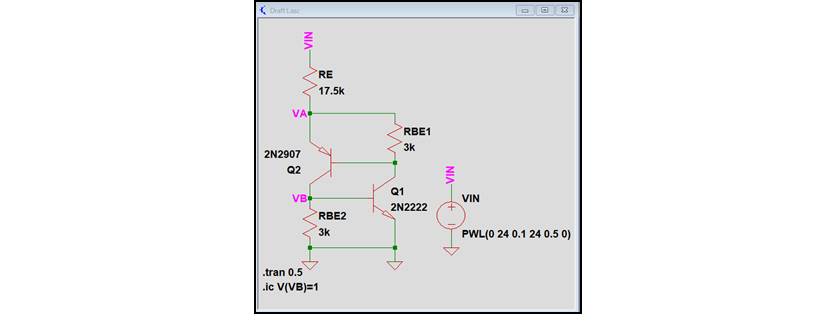

シミュレーション回路

LTspiceを用いて、ラッチが解除される電圧\(V_{IN(RE)}\)が8Vになっているかを確認してみます。上図にシミュレーション回路を示します。『.icコマンド』を使用してトランジスタ\(Q_{1}\)のベース電圧\(V_B\)を初期値を1Vに設定することで強制的にラッチ動作をさせています。供給電圧\(V_{IN}\)は0.1秒まで24Vであり、0.1秒を超えると電圧が低下するように設定しています。

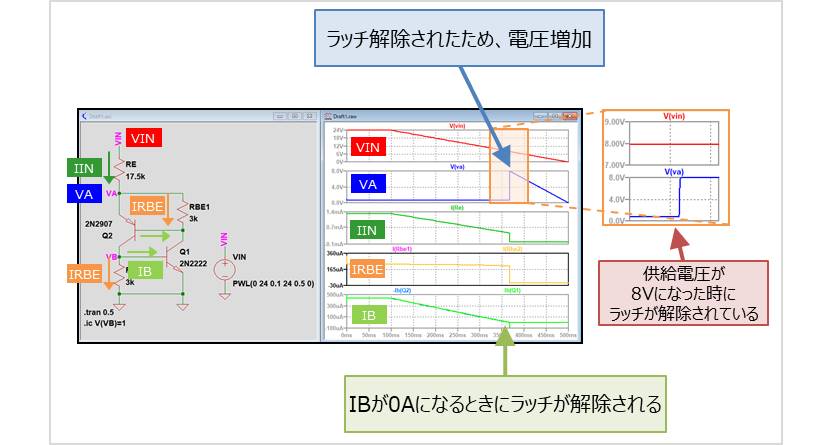

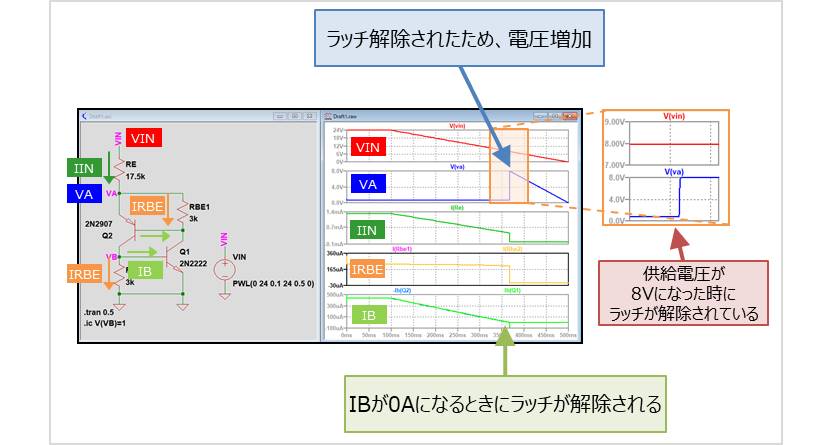

シミュレーション結果

シミュレーション結果を上図の右に示します。供給電圧\(V_{IN}\)が8Vになった時に電圧\(V_{A}\)が増加していることから、ラッチが解除される電圧\(V_{IN(RE)}\)が設計通りの8Vになっていることが確認できます。また、ベース電流\(I_{B}\)が0Aになっている時にラッチが解除していることも確認できます。

まとめ

この記事ではラッチ回路の抵抗値の設計方法について説明しました。設計において、抵抗\(R_{IN}\)と抵抗\(R_{BE}\)を適切に設定しないと以下のようになるため注意してください。

- 抵抗\(R_{IN}\)が大きく、抵抗\(R_{BE}\)が小さい場合

- 抵抗\(R_{IN}\)が小さく、抵抗\(R_{BE}\)が大きい場合

供給電圧\(V_{IN}\)が少し低下しただけで、ベース電流\(I_{B}\)が0Aとなり、ラッチ解除してしまう場合があります。

トランジスタに流れる電流が絶対最大定格を超える場合があります。また、電圧\(V_{A}\)が高くなるため、そもそもラッチ動作が成り立たない場合があります。

また、当サイトの全記事一覧は以下にまとめてあるのでぜひ参考にしてください。