この記事ではJFETを用いた『定電流回路』について

- JFETを用いた『定電流回路』の回路図

- 定電流回路の原理

- 定電流値の導出方法

などを図を用いて分かりやすく説明するように心掛けています。ご参考になれば幸いです。

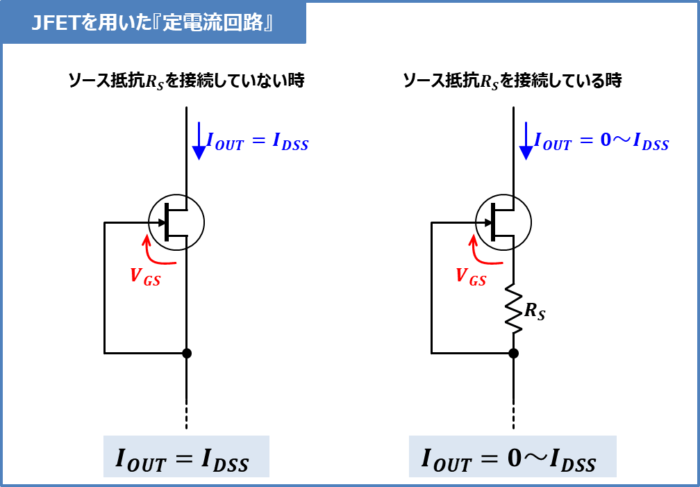

JFETを用いた『定電流回路』

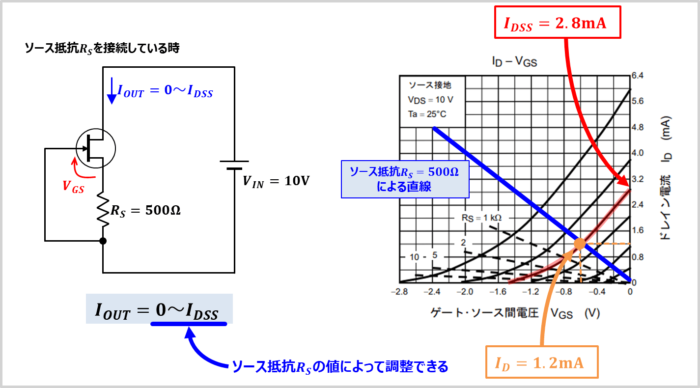

上図はNチャネル型の接合型FET(JFET)を用いた定電流回路です。JFETのソース端子に抵抗RSを接続することで定電流値を調整することができます。

この回路の定電流値IOUTは次式で表されます。

定電流値の式

- ソース端子に抵抗RSを接続しない時

- ソース端子に抵抗RSを接続している時

\begin{eqnarray}

I_{OUT}=I_{DSS}

\end{eqnarray}

\begin{eqnarray}

I_{OUT}=0~I_{DSS}

\end{eqnarray}

上式において、IDSSはゲートとソースが等電位(ゲートソース間電圧VGSが0V)の場合におけるドレイン電流です。

次に『回路の原理』と『上式の導出方法』について説明します。

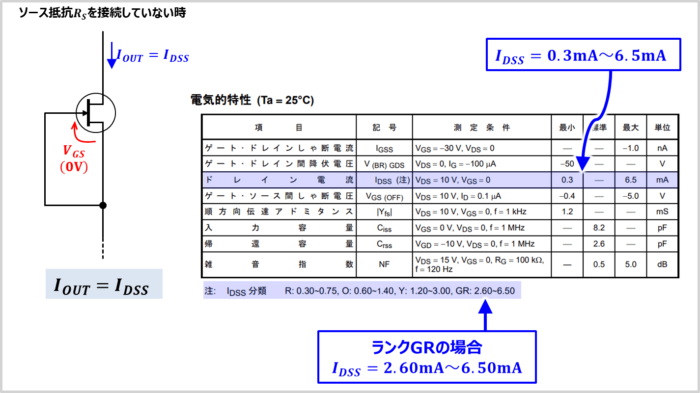

定電流値IOUTの導出方法(ソース端子に抵抗RSを接続しない時)

ソース端子に抵抗RSを接続しない場合、JFETのゲートソース間電圧VGSが0Vとなります。

そのため、JFETに流れる電流はドレイン電流IDSSとなります。なお、IDSSはゲートとソースが等電位(ゲートソース間電圧VGSが0V)の場合におけるドレイン電流です。

また、上図に示した回路において、ドレイン電流IDSSと定電流値IOUTは等しいため、次式が成り立ちます。

\begin{eqnarray}

I_{OUT}=I_{DSS}

\end{eqnarray}

上図に示しているのは東芝製JFET(2SK30ATM)のデータシートの一部です。ドレイン電流IDSSはドレインソース間電圧VDSが10V、ゲートソース間電圧VGSが0Vの時に0.3mA~6.5mAになっていることが分かります。このようにドレイン電流IDSSにはバラツキがあります。また、ドレイン電流IDSSは温度によっても変化します。

なお、JFETには様々なランクがあります。東芝製JFET(2SK30ATM)の場合にはR,O,Y,GRのランクがあり、各ランクによりドレイン電流IDSSが異なります。ランクRのJFETを使用した場合には『IDSS=0.30mA~0.75mA』、ランクGRのJFETを使用した場合には『IDSS=2.60mA~6.50mA』となります。電気的特性の表に記載されている『ドレイン電流IDSS=0.3mA~6.5mA』は全てのランクを含んだ場合の値となっています。

例えば、ランクGRの東芝製JFET(2SK30ATM)を使用している場合、定電流値IOUTは『IDSS=2.60mA~6.50mA』のいずれかになります

補足

- JFETはゲートソース間電圧VGSが0Vの時にドレイン電流が最大(IDSS)となります。

- IDSSは『ドレイン遮断電流』と呼ばれています。

- 定電流ダイオードはJFETのゲート端子(G)とソース端子(S)を接続し、ドレイン端子(D)をアノード(A)、ソース端子(S)をカソード(K)にした素子です。

定電流値IOUTの導出方法(ソース端子に抵抗RSを接続した時)

JFETのドレイン電流IDSSにはバラツキがあります。そこで、電流を所望の値に調整するためにソース抵抗RSを接続して使用するのが一般的です。

一例として、ランクGRの東芝製JFET(2SK30ATM)を使用する場合を考えてみましょう。

ソース抵抗RSを接続しないと、定電流値IOUTは『IDSS=2.60mA~6.50mA』のいずれかになります。しかし、ソース抵抗RSを接続することで、定電流値IOUTを2.60mA~6.50mAより低い電流値に設定することができます。

ここで、一例として上図に直流電源VIN=10V、JFET(IDSS=2.8mA品)、ソース抵抗RS=500Ωで構成された定電流回路を示しています。

この定電流回路は下記の動作を行っています。

- ドレイン電流IDが増加する

- ソース抵抗RSでの電圧降下が増加する

- JFETのゲートソース間電圧VGSが減少する(0Vから遠ざかる)

- ドレイン電流IDが減少する

- ソース抵抗RSでの電圧降下が減少する

- JFETのゲートソース間電圧VGSが増加する(0Vに近づく)

- ドレイン電流IDが増加する(①と同じ)

- ソース抵抗RSでの電圧降下が増加する(②と同じ)

上記の動作が繰り返されることにより定電流動作をしています。すなわち、ソース抵抗RSを接続することで、ドレイン電流IDの平衡点ができるということになります。

この平衡点を求めるためにJFETの「ID-VGS特性」を用います。

ソース抵抗RSに流れるドレイン電流IDが増加すると、ゲートソース間電圧VGSが減少するため、「ID-VGS特性」のグラフ上に「ソース抵抗RSによる直線(上図の青線)」を描くことができます。この「ID-VGS特性」と「ソース抵抗RSによる直線(上図の青線)」の交点が回路の平衡点となります。例えば、IDSS=2.8mAのJFETを使用していると、ドレイン電流IDは1.2mAで平衡します。

この定電流回路において、ドレイン電流IDと定電流値IOUTは等しくなるため、次式が成り立ちます。

\begin{eqnarray}

I_{OUT}=I_D=1.2{\mathrm{[mA]}}

\end{eqnarray}

なお、定電流値IOUTはソース抵抗RSの値により調整することができ、0~IDSSの範囲となります。

補足

- 先ほど説明したソース抵抗RSを接続していない定電流回路よりも、流すことが出来る電流が小さくなります。それは、ソース抵抗RSを接続することでゲートソース間電圧VGSが減少する(0Vからマイナス方向になる)からです。

- ソース抵抗RSには数100Ω程度の抵抗を入れることが多いです。

- ソース抵抗RSには半固定抵抗を使用してもOKです。

まとめ

この記事ではJFETを用いた『定電流回路』について、以下の内容を説明しました。

- JFETを用いた『定電流回路』の回路図

- 定電流回路の原理

- 定電流値の導出方法

お読み頂きありがとうございました。

当サイトでは電気に関する様々な情報を記載しています。当サイトの全記事一覧は以下のボタンから移動することができます。

また、下記に当サイトの人気記事を記載しています。ご参考になれば幸いです。