ラッチ回路(自己保持回路)とは一度スイッチをオンしたら、そのスイッチをオフしてもオン状態を保持する回路のことです。

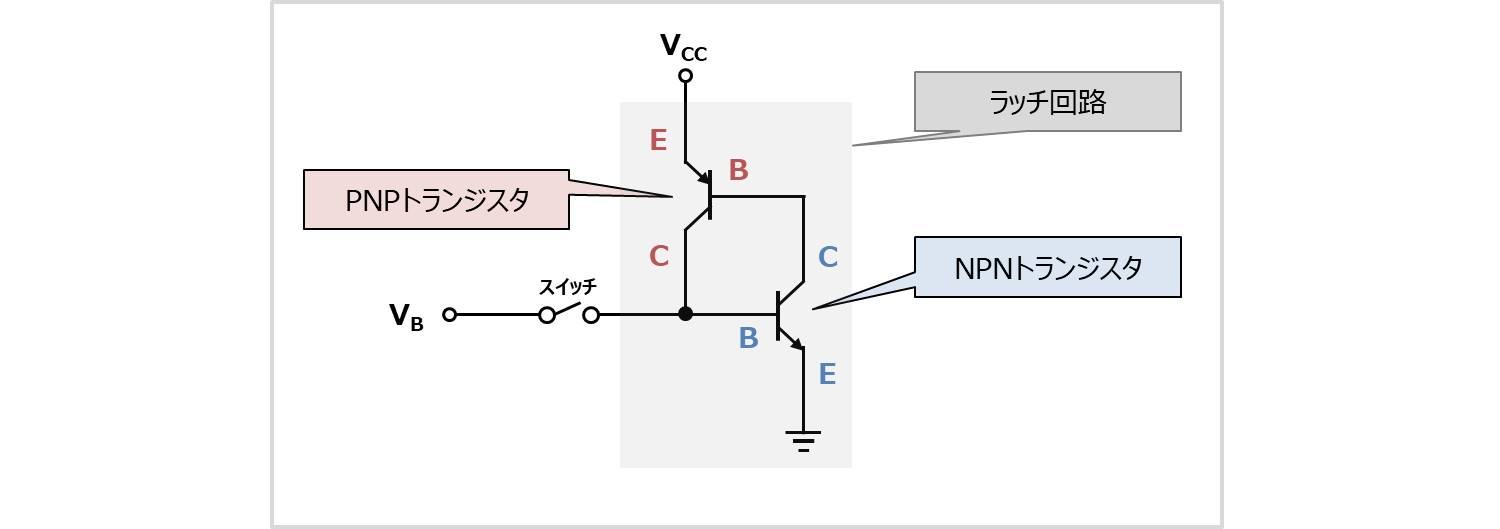

今回はNPNトランジスタとPNPトランジスタの2つを使用したラッチ回路について説明します。

トランジスタを使用したラッチ回路の回路形態

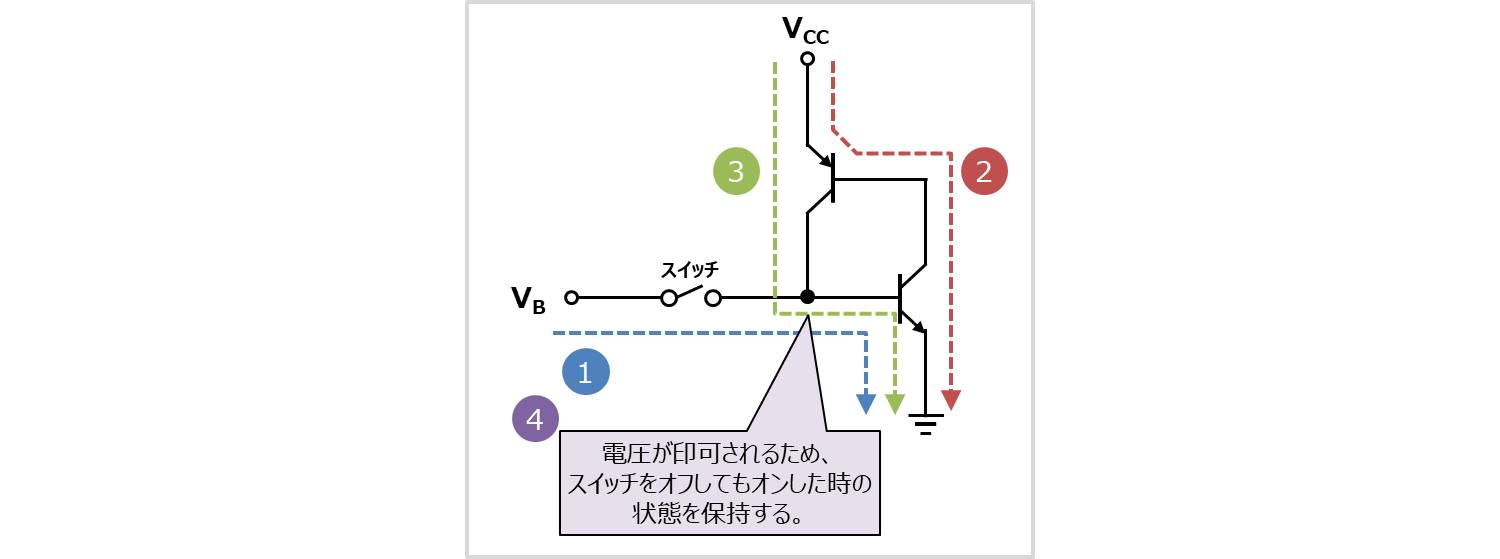

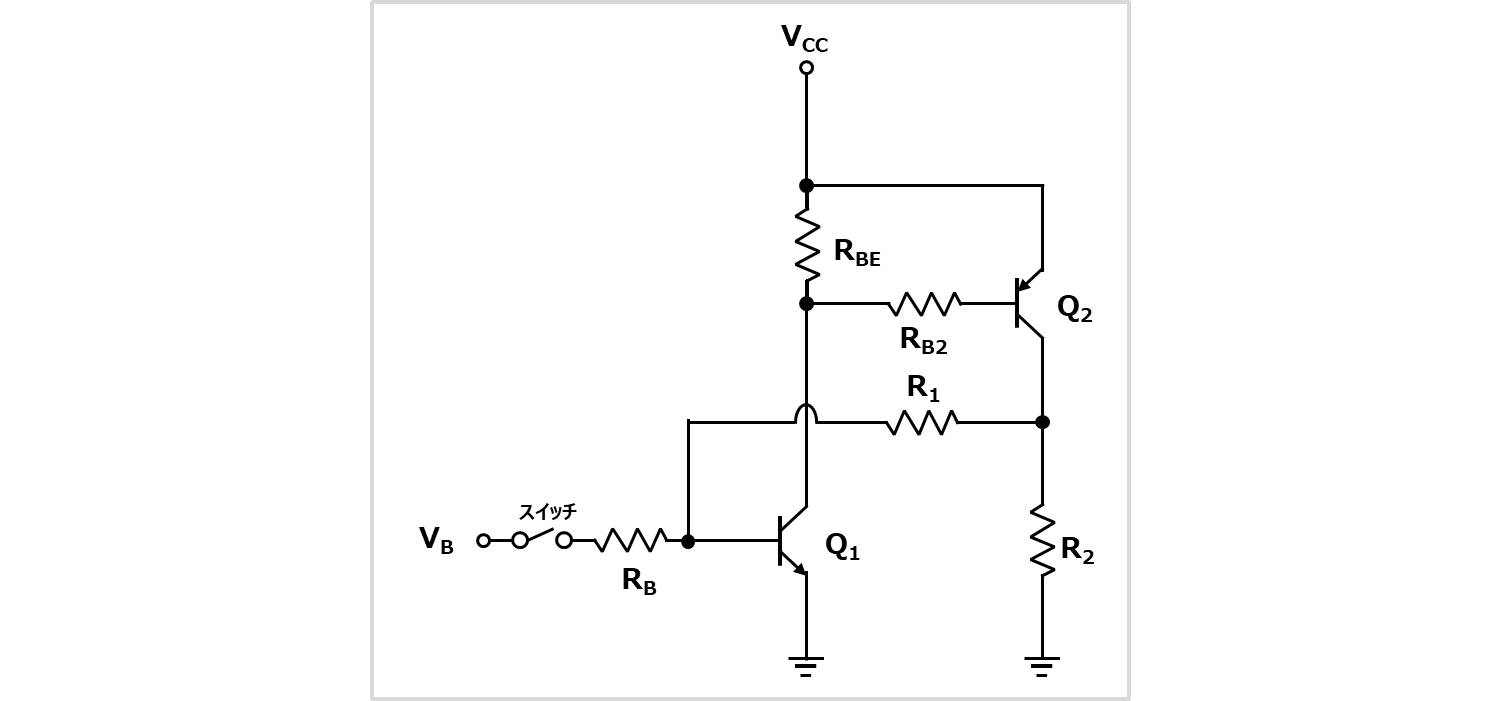

NPNトランジスタとPNPトランジスタの2つを使用したラッチ回路は上図のようになっています。

上の回路図はラッチ回路の動作をイメージするためだけの回路であり、実際には電流を制限する抵抗が接続されます(この記事の後半に抵抗の接続箇所について記載しています)。

ラッチ回路の回路図の覚え方

ラッチ回路の回路図を以下の順番で描くと覚えやすいです。

- NPNトランジスタのベース(B)をPNPトランジスタのコレクタ(C)へ接続します。

- PNPトランジスタのベース(B)をNPNトランジスタのコレクタ(C)に接続します。

- NPNトランジスタのエミッタ(E)をGNDに接続します。

- PNPトランジスタのエミッタ(E)を電圧VCCに接続します。

- NPNトランジスタのベース(B)にはスイッチを接続します。

ラッチ回路の動作

- スイッチをオンすると、NPNトランジスタのベース(B)に電流が流れます。

- NPNトランジスタのベース(B)に電流が流れることでNPNトランジスタはオンし、PNPトランジスタのエミッタ(E)からNPNトランジスタに向かって電流が流れます。

- PNPトランジスタのベース(B)に電流が流れることで、PNPトランジスタはオンし、PNPトランジスタのエミッタ(E)からNPNトランジスタのベース(B)に向かって電流が流れます。

- その結果、NPNトランジスタのベース(B)には電圧が印加されるので、スイッチをオフしてもオンした時の状態が保持されます。

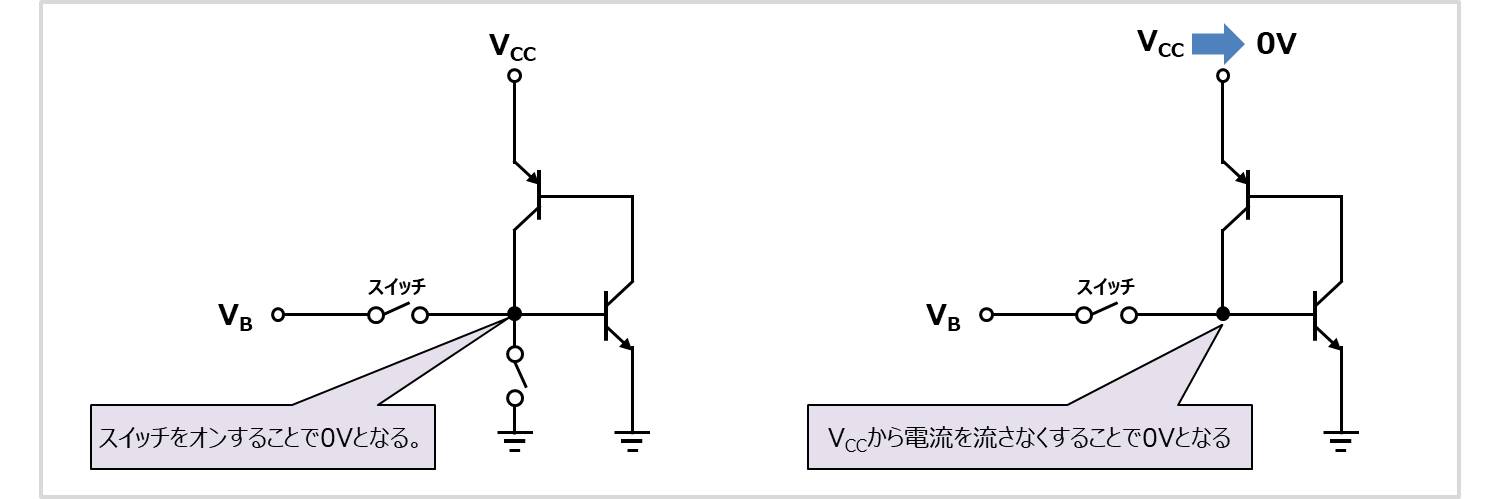

ラッチ回路の解除方法

スイッチをオフしてもオンした時の状態が保持されますが、この保持を解除する方法が2つあります。

- NPNトランジスタのベース(B)にスイッチを接続し、そのスイッチをオフする

- PNPトランジスタのエミッタ(E)に電流を流さなくする

NPNトランジスタがオフされ、PNPトランジスタのエミッタ(E)からNPNトランジスタに向かって電流を流すことができず、PNPトランジスタがオフします。

電圧VCCを0Vとすると、NPNトランジスタのベース(B)に電圧が印可されないため、NPNトランジスタがオフされ、PNPトランジスタのエミッタ(E)からNPNトランジスタに向かって電流を流すことができず、PNPトランジスタがオフします。

実際のラッチ回路には電流制限の抵抗が必要

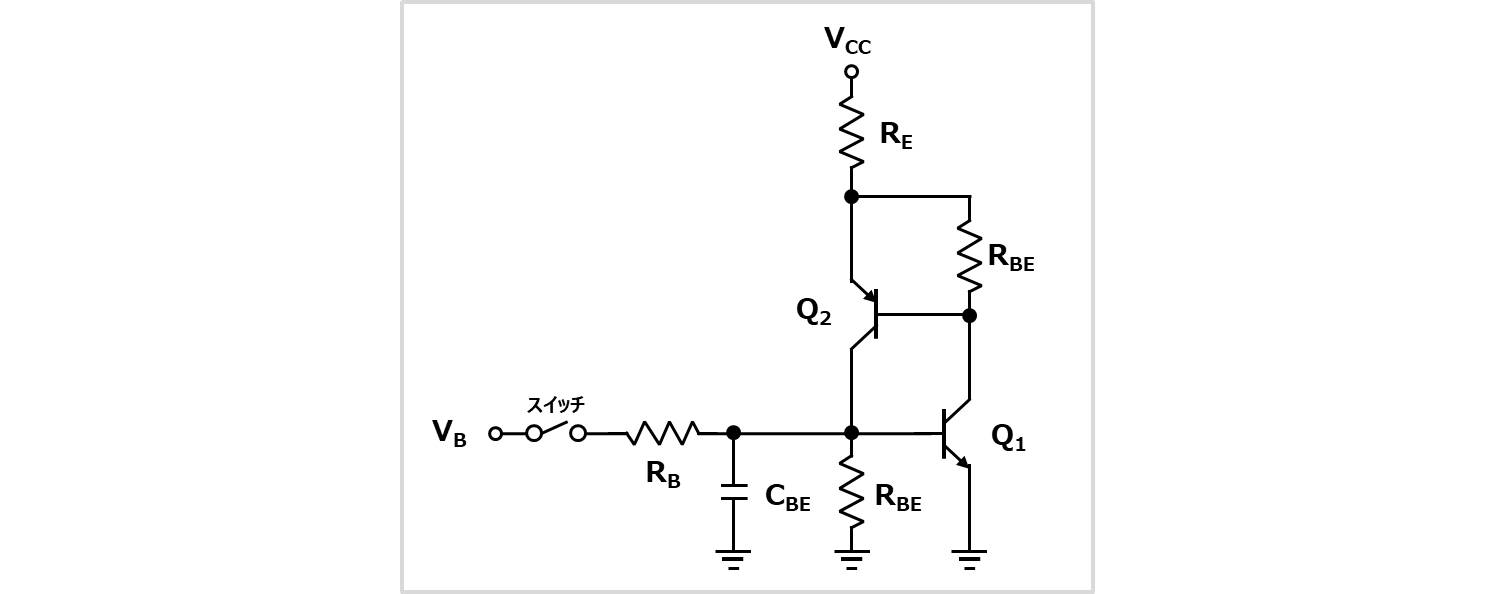

今まで示した回路図はラッチ回路の動作を理解するためだけの回路図です。実際には使用することができません。

使用するには、トランジスタに流れる電流を制限する抵抗が必要になります。

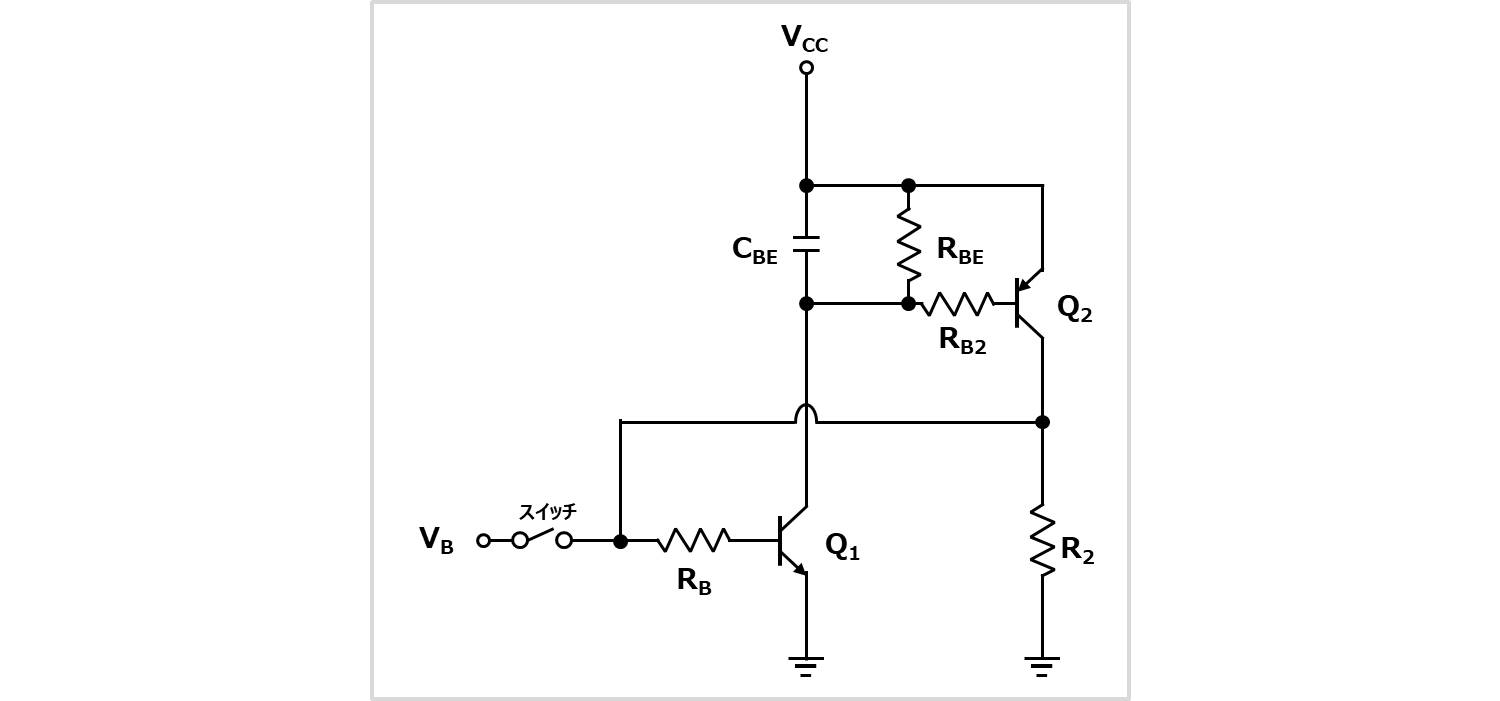

回路はこのようになります(これは一例です)。

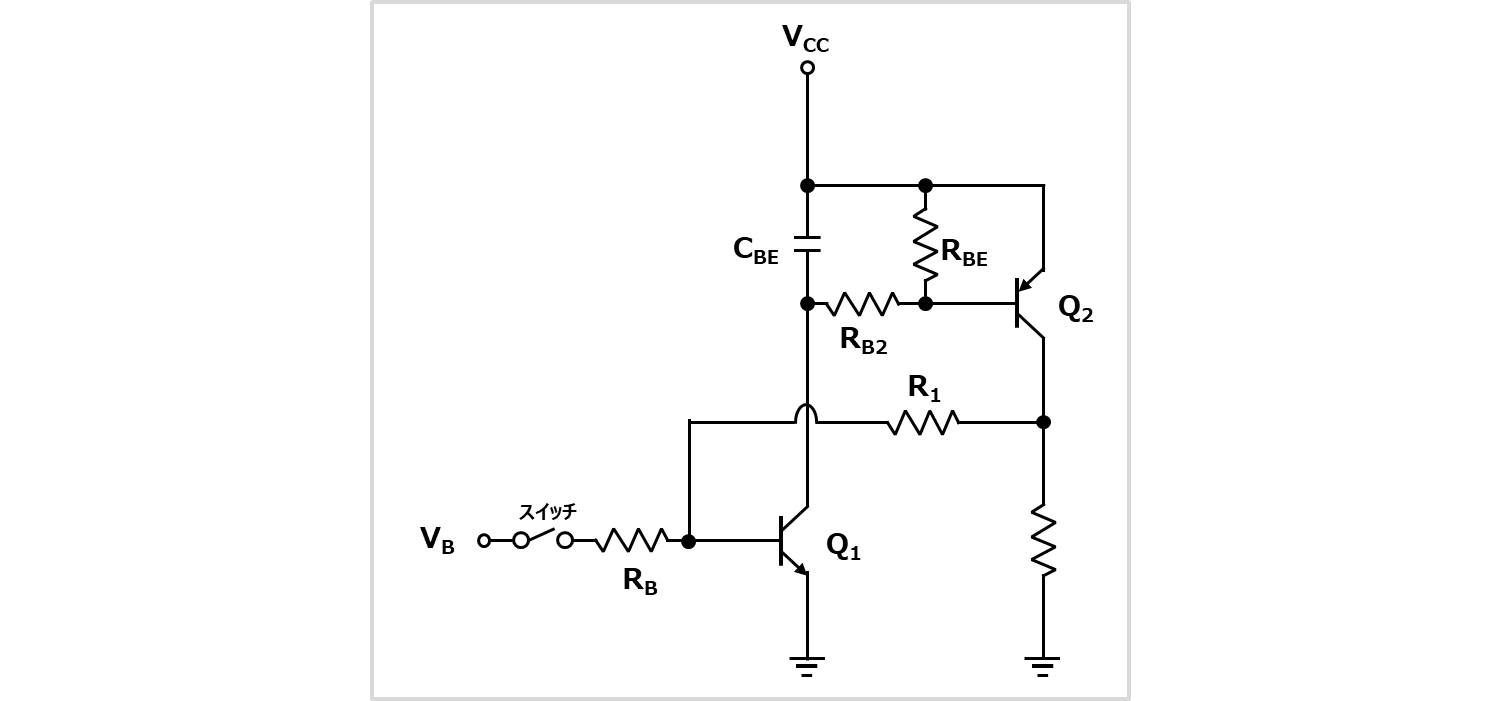

各抵抗とコンデンサの意味は以下の通りです。

- RB:NPNトランジスタのベース電流制限用抵抗。スイッチから静電気放電が入ってきた時にトランジスタを保護する抵抗。

- CBE:スイッチから静電気放電が入ってきた時にトランジスタを保護する容量。

- RBE:ベースから入ってくるノイズによる誤動作を防ぐ抵抗。

- RE:PNPトランジスタのエミッタに流れる電流抑制用抵抗。

【補足】さまざまなラッチ回路を紹介

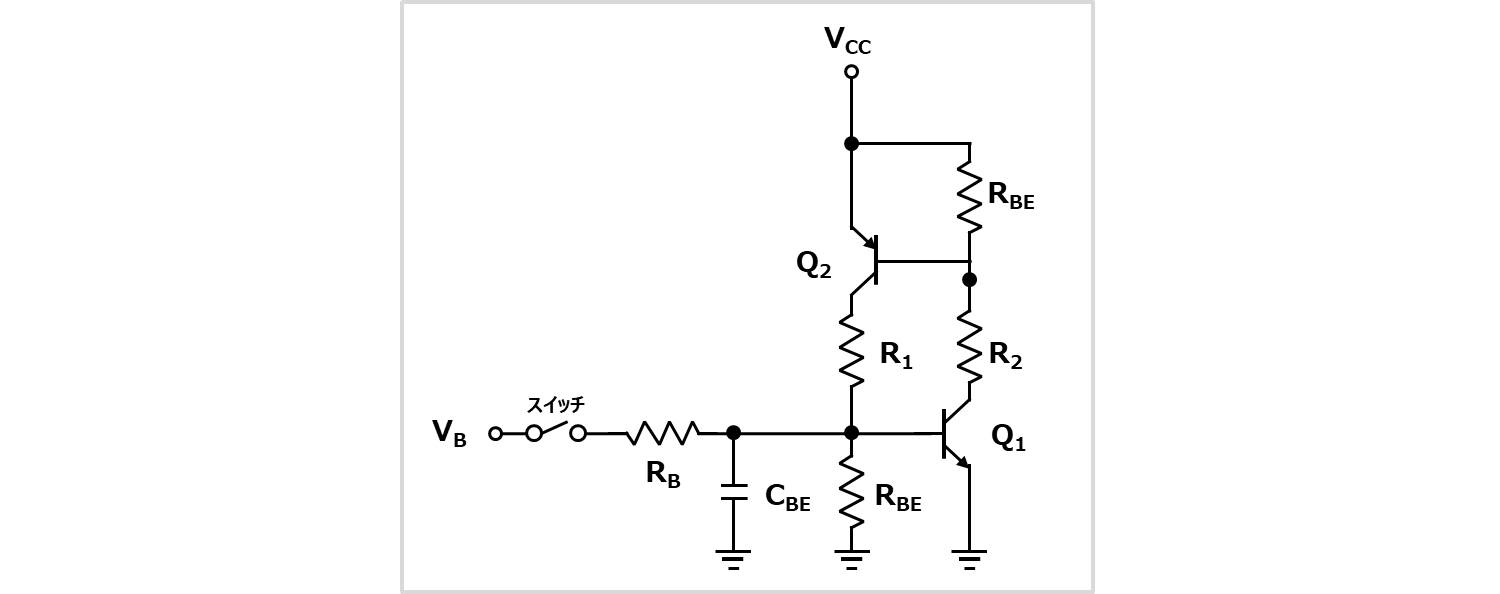

ラッチ回路の回路形態において、抵抗の位置などは特に決まりはありません。トランジスタに流れる電流を制限するという目的ならどこに接続しても大丈夫です。

そのため同じラッチ回路でも様々な回路形態があるんです。ネットで調べると沢山出てきます。

回路1

抵抗REがなくなり、代わりにQ1のコレクタと、Q2のコレクタに抵抗を配置しています。

回路2

見た感じは回路1と異なりますが、動作は同じになります。

回路3

回路4